# **ADVANCE PROGRAM**

2015 IEEE INTERNATIONAL SOLID-STATE CIRCUITS CONFERENCE

FEBRUARY 22, 23, 24, 25, 26

**CONFERENCE THEME:**

# SILICON SYSTEMS SMALL CHIPS FOR BIG DATA

SAN FRANCISCO MARRIOTT MARQUIS HOTEL

THURSUAY ALL-UAY Forums: Advances in Wireless Power; Low Power Fo 10e; rf transmitter Advances; 10 @ 2568/s & More

**JRSE:** CMOS LOW-VOLTAGE CIRCUIT DESIGN

HGH-SP

DN GRADUATE STUDENT BESEARCH IN PROGRESS. ICs TALKING TO NEURONS

2 EVENING EVENTS (

5-DAY Progran

### **ISSCC VISION STATEMENT**

The International Solid-State Circuits Conference is the foremost global forum for presentation of advances in solid-state circuits and systems-on-a-chip. The Conference offers a unique opportunity for engineers working at thecutting edge of IC design and application to maintain technical currency, and to network with leading experts.

### **CONFERENCE TECHNICAL HIGHLIGHTS**

On **Sunday, February 22<sup>nd</sup>**, the day before the official opening of the Conference, ISSCC 2015 offers:

- A choice of up to 4 of a total of 10 Tutorials

- A choice of 1 of 2 all-day Advanced-Circuit-Design Forums

The 90-minute tutorials offer background information and a review of the basics in specific circuit-design topics. In the all-day Advanced-Circuit-Design Forums, leading experts present state-of-the-art design strategies in a workshop-like format. The Forums are targeted at designers experienced in the technical field.

On Sunday evening, there are two events: A Special-Topic Session entitled, "**Brain-Machine Interfaces: ICs Talking to Neurons**" will be offered starting at 8:00pm. In addition, the **Student Research Preview**, featuring short presentations followed by a poster session from selected graduate-student researchers from around the world will begin at 7:30 pm. Introductory remarks at the Preview will be provided by a distinguished member of the solid-state circuit community.

On Monday, February 23<sup>rd</sup>, ISSCC 2015 offers three plenary papers on the theme: "Silicon Systems - Small Chips for Big Data". On Monday at 12:15 pm, there will be a Women's Networking Event, a luncheon. On Monday afternoon, there will be five parallel technical sessions, followed by a Social Hour open to all ISSCC attendees. The Social Hour, held in conjunction with the Book Display and Author Interviews, will also include a **Demonstration Session**, featuring posters and live demonstrations for selected papers from industry and academia. Monday evening will include 2 panel sessions on "Moore's Law Challenges Below 10nm..." and "Lost Art? Neat Circuit Tricks with Fewer than a Dozen Transistors".

On **Tuesday, February 24**<sup>th</sup>, there are five parallel technical sessions, both morning and afternoon. A Social Hour open to all ISSCC attendees will follow. The Social Hour, held in conjunction with the Book Display and Author Interviews, will also include a second **Demonstration Session**. Tuesday evening sessions include both a panel on "**Innovating on the Tapeout Treadmill**", as well as a Special-Topic Session on "**How to Achieve 1000× More Wireless-Data Capacity. 5G**?".

On **Wednesday, February 25<sup>th</sup>**, there will be five parallel technical sessions, both morning and afternoon, followed by Author Interviews.

On Thursday, February 26th, ISSCC offers a choice of five all-day events:

- A Short Course on "Circuit Design in Advanced CMOS Techniques:

- How to Design with Lower Supply Voltages" • Four Advanced-Circuit-Design Forums on

- "Cutting the Last Wire Advances in Wireless Power";

- "Building the Internet of Everything (IoE):

- Low-Power Techniques at the Circuit & Systems Level";

- "Advanced RF CMOS Transmitter Techniques ";

- "IO Design at 25Gb/s & Beyond".

Registration for educational events on Sunday and Thursday will be filled on a first-come first-served basis. Use of the ISSCC Web-Registration Site (http://www.isscc.org) is strongly encouraged. Registrants will be provided with immediate confirmation on registration for the Conference, Tutorials, Advanced-Circuit-Design Forums, and the Short Course.

## Need Additional Information? Go to: www.isscc.org

## **TABLE OF CONTENTS**

| Tutoria  | ls4·                                                                            | 7  |

|----------|---------------------------------------------------------------------------------|----|

|          | FORUMS                                                                          |    |

| F1<br>F2 | High-Speed Interleaved ADCs<br>Memory Trends: From Big Data to Wearable Devices | 8  |

|          | EVENING SESSIONS                                                                |    |

| ES1      | Student Research Preview                                                        | 0  |

| ES2      | Brain-Machine Interfaces:<br>Integrated Circuits Talking to Neurons1            | 1  |

|          | PAPER SESSIONS                                                                  |    |

| 1        | Plenary Session                                                                 | 3  |

| 2<br>3   | RF TX/RX Design Techniques                                                      |    |

| 4        | Processors                                                                      | 6  |

| 5        | Analog Techniques1                                                              | 7  |

| 6        | Image Sensors and Displays1                                                     | 8  |

| Demon    | stration Session1                                                               | 9  |

|          | EVENING SESSIONS                                                                |    |

| EP1      | Moore's Law Challenges Below 10nm:                                              |    |

| FP2      | Technology, Design and Economic Implications                                    | 0. |

|          |                                                                                 |    |

|          | PAPER SESSIONS                                                                  |    |

| 7        | Non-Volatile Memory Solutions                                                   | 1  |

| 8<br>9   | Low-Power Digital Techniques                                                    | 2  |

| 10       | Advanced Wireline Techniques and PLLs                                           | 4  |

| 11       | Sensors and Imagers for Life Sciences                                           | 5  |

| 12<br>13 | Inductor-Based Power Conversion                                                 | .6 |

| 13       | Energy-Efficient RF Systems                                                     |    |

| 15       | Data-Converter Techniques                                                       | 9  |

| 16       | Emerging Technologies Enabling Next-Generation Systems                          | 0  |

| Demon    | stration Session                                                                | 1  |

####

|     | EVENING SESSIONS                                      |  |

|-----|-------------------------------------------------------|--|

| EP3 | Innovating on the Tapeout Treadmill                   |  |

| ES3 | How to Achieve 1000× more Wireless Data Capacity? 5G? |  |

#### PAPER SESSIONS

| 17 | Embedded Memory and DRAM I/O                       | 35 |

|----|----------------------------------------------------|----|

| 18 | SoCs for Mobile Vision, Sensing and Communications |    |

| 19 | Advanced Wireless Techniques                       |    |

| 20 | Energy Harvesting and SC Power Conversion          |    |

| 21 | Innovative Personalized Biomedical Systems         |    |

| 22 | High-Speed Optical Links                           | 40 |

| 23 | Low-Power SoCs                                     | 41 |

| 24 | Secure, Efficient Circuits for IoT                 | 42 |

| 25 | RF Frequency Generation from GHz to THz            | 43 |

| 26 | Nyquist-Rate Converters                            | 44 |

| 27 | Physical Sensors                                   | 45 |

|    |                                                    |    |

#### SHORT COURSE

|                        | Circuit Design in Advanced CMOS Technologies:<br>How to Design with Lower Supply Voltages | 46-48 |  |

|------------------------|-------------------------------------------------------------------------------------------|-------|--|

|                        | FORUMS                                                                                    |       |  |

| F3<br>F4               | Cutting the Last Wire – Advances in Wireless Power                                        | 49    |  |

| F4                     | Building the Internet of Everything (IoE):                                                |       |  |

|                        | Low-Power Techniques at the Circuit and System Levels                                     |       |  |

| F5                     | Advanced RF CMOS Transmitter Techniques                                                   | 51    |  |

| F6                     | I/O Design at 25Gb/s and Beyond:                                                          |       |  |

|                        | Enabling the Future Communication Infrastructure for Big Data                             | 52    |  |

| Comm                   | ittees                                                                                    | 53-57 |  |

| Conference Information |                                                                                           | 58-61 |  |

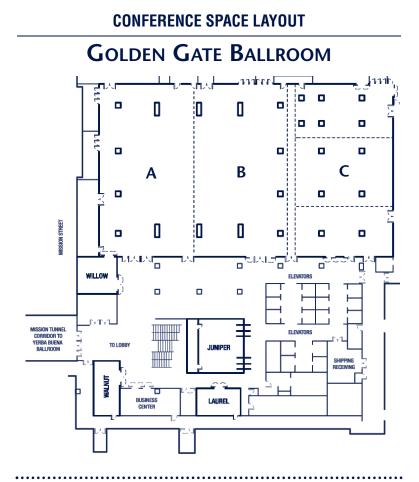

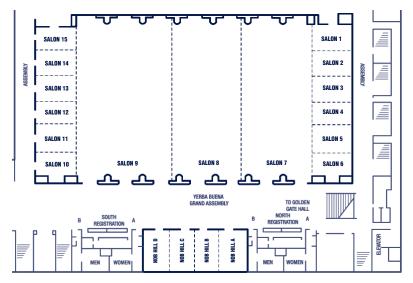

| Confer                 | Conference Space Layout                                                                   |       |  |

|                        |                                                                                           |       |  |

## Sunday February 22<sup>nd</sup>

#### T1: Fundamentals of Modern RF Receivers

To be compliant with multi-standard applications, the RF front-end of a modern transceiver must satisfy several challenging tasks such as large operative bandwidth, low noise, and high linearity. Over the years, addressing such requirements has significantly changed the radio architecture towards an ultimate solution based on current signal processing and passive mixers. In this tutorial, after a brief description of the typical structure of a receiver, the main properties that the radio must satisfy will be defined. After that, voltage and current signal processing will be compared showing why a fully current-mode approach is more suitable in deep-scale technologies. The tutorial will end by describing the most popular RF front-end architectures with a particular emphasis on the noise-canceling technique and the Class-AB solutions.

#### Instructor: Antonio Liscidini

Antonio Liscidini received the Laurea degree and Ph.D. in Electrical Engineering from the University of Pavia, Pavia, Italy, in 2002 and 2006 respectively. He was a summer intern at National Semiconductor in 2003 (Santa Clara, CA) studying polyphase filters and CMOS LNAs. From 2008 to 2012 he was Assistant Professor at the University of Pavia and consultant for Marvell Semiconductor in the area of integrated circuit design. In December 2012 he joined the Edward S. Rogers Sr. Department of Electrical & Computer Engineering of the University of Toronto. His research interests are in the implementations of transceivers and frequency synthesizers for cellular and ultra-low-power applications.

#### **T2: Basics of DRAM Interfaces**

Memories have evolved continuously since the simple days of SDRAM. Back then, one interface standard was dominating and could be adapted to the different system needs. Now, one size no longer fits all. The number of DRAM standards is proliferating since different system environments require different, tailored DRAM-solutions. Examples are DDRn, GDDR5, HBM, LPDDRn, and WIOn. In this tutorial, we give an overview of these interface standards highlighting important details of the specifications, and describe selected design aspects and their system level implications.

#### Instructor: Martin Brox

Martin Brox received Dipl. and Dr. degrees from the University of Münster in 1988 and 1992. In 1988 he joined Siemens Corporate Research for a project to improve the modeling of hot-carrier degradation on CMOS-circuits. In 1992, he moved to the IBM/Siemens/Toshiba DRAM development alliance initially focusing on design, layout and test of DRAM mini-arrays and later DRAM-design. In 1997, he joined Siemens Semiconductor which later became Infineon and Qimonda where he was responsible for multiple commodity, RDRAM, GDDR3 and GDDR5 designs. In 2009 he joined Elpida (now part of Micron) as the lead design engineer for Micron's GDDR5 development.

#### T3: Ultra-Low-Power Wireless Systems

Emerging applications such as wearable devices, sensor networks and the 'internet of things' have to operate from very limited power budgets, and thus ultra-low-power operation is becoming increasingly important. This tutorial will address a range of issues that need to be considered in the design of ultra-low-power wireless systems. The tutorial will describe key features of low-power wireless standards such as BTSmart. We will then give an overview of architectures appropriate for very low power implementation including super-regenerative receivers, BAW-based architectures and direct modulation transmitters, and will outline the system trade-offs, which need to be considered for specific applications. We will then consider some key circuit building blocks required in the receiver, transmitter, and peripheral units and outline design techniques that are suitable for very low power implementation.

## Sunday February 22<sup>nd</sup>

#### Instructor: Alison Burdett

Alison Burdett has over 25 years of experience in semiconductor design. She joined Toumaz in 2001 as Technical Director, and is currently responsible for delivering silicon and healthcare technology programs within the company. Prior to joining Toumaz, Alison spent time both in industry as an integrated circuit designer, and also in academia (as Senior Lecturer in Analogue IC Design at Imperial College London) Dr. Burdett is a Chartered Engineer, a Fellow of the Institute of Engineering and Technology (FIET) and a Senior Member of the IEEE. She is European Regional Chair of the Technical Program Committee for the IEEE International Solid State Circuits Conference (ISSCC), a member of the National Microelectronics Institute of Biomedical Engineering, Imperial College.

#### T4: Low-Power Near-threshold Design

Digital circuit energy efficiencies plateaued due to stagnated voltage scaling in sub-90nm technologies. As a result, there is renewed interest in operating circuits at low supply voltages, such as near the device threshold voltage (referred to as near-threshold or NT design). NT operation offers a good balance between performance and energy efficiency, in contrast to sub-threshold design, which sacrifices performance for energy optimality. This tutorial offers design guidelines for near-threshold operation, particularly related to NT design robustness. Design examples from both academia and industry will highlight DSP accelerators, embedded memories, wide-range voltage scalable designs, and variability compensation strategies that scale to NT voltages.

#### Instructor: Dennis Sylvester

Dennis Sylvester received a Ph.D. from the University of California, Berkeley and is Professor of Electrical Engineering and Computer Science at the University of Michigan, Ann Arbor, MI. He has published over 375 articles along with one book and several book chapters, and holds 20 US patents. His research interests include the design of millimeter-scale computing systems and energy-efficient near-threshold computing. He is co-founder of Ambiq Micro, a fabless semiconductor company developing ultra-low-power mixed-signal solutions for compact wireless devices. He is an IEEE Fellow.

#### **T5: High-Speed Current-Steering DACs**

Among the various existing digital-to-analog converter (DAC) architectures, the currentsteering DAC architecture prevails at high sampling rates. Its simple underlying topology makes these DACs well-suited for implementation in deep-submicron CMOS processes, where high-speed switches are readily available. The topological simplicity, however, comes with a substantial sensitivity to many sources of distortion. This tutorial first summarizes the basics of the current-steering architecture. Subsequently, it covers the various distortion mechanisms as well as the design techniques available to overcome their detrimental effects on DAC performance. Finally, measurement techniques required to assess the performance of the eventual DAC design are treated.

#### Instructor: Jan Mulder

Jan Mulder received the M.Sc. and Ph.D. degrees in electrical engineering from Delft University of Technology, The Netherlands, in 1994 and 1998, respectively. From 1998 to 2000, he was with Philips Research Laboratories, Eindhoven, The Netherlands. In 2000, he joined Broadcom, Bunnik, The Netherlands, where he has been involved in analog and mixedsignal IC design. He has published over 60 papers and holds more than 35 U.S. patents in circuit design. He served as an Associate Editor for IEEE Trans. on CAS-1 and is a member of the ISSCC ITPC.

## Sunday February 22nd

#### **T6: Clock and Data Recovery Architectures and Circuits**

This tutorial provides ground theory and practical strategies for the design of clock-anddata-recovery circuits. We begin by relating performance metrics such as jitter transfer, jitter tolerance, and jitter peaking to CDR loop components and use these relationships to elucidate application-specific design challenges and tradeoffs. Following this, we will discuss both architectural- and circuit-level techniques to manage/overcome these tradeoffs. Specifically, we would compare different architectures: bang-bang vs. linear, digital vs. analog vs. hybrid loops, oscillator vs. phase interpolator, and reference-less vs. reference-based CDRs.

#### Instructor: Pavan Kumar Hanumolu

Pavan Kumar Hanumolu is an Associate Professor in the Department of Electrical and Computer Engineering at the University of Illinois, Urbana-Champaign. He received the Ph.D. degree from the School of Electrical Engineering and Computer Science at Oregon State University, Corvallis, in 2006, where he subsequently served as a faculty member until 2013. Dr. Hanumolu's research interests are in energy-efficient integrated circuit implementation of analog and digital signal processing, wireline communication systems, and power conversion. He currently serves as an Associate Editor of the Journal of Solid-State Circuits, and is a technical program committee member of the VLSI Circuits Symposium, and International Solid-State Circuits Conference

#### **T7: Basics of Many-Core Processors**

This tutorial focuses on the design of many-core processors spanning clients to servers to high-performance computing systems in scaled CMOS process. Key circuits and design techniques are highlighted for robust and variation-tolerant logic, embedded memory arrays and on-die interconnect fabrics. Also presented are design principles that enable a wide dynamic voltage-frequency operating range, spanning multi-threaded high-throughput near-threshold voltage to single-threaded burst performance modes. Fine-grain multi-voltage design and power management techniques are covered, along with smart variation-aware workload mapping schemes to achieve maximum performance under stringent thermal and energy constraints. Real chip design examples are used to illustrate basic design principles and practical considerations.

#### **Instructor: Vivek De**

Vivek De is an Intel Fellow and Director of Circuit Technology Research in Intel Labs. He is responsible for providing strategic technical directions for long-term research in future circuit technologies and leading energy efficiency research across the hardware stack. He has 223 publications in refereed international conferences and journals and 195 patents, with 30 more patents filed (pending). He received an Intel Achievement Award for contributions to integrated voltage regulator technology. He received a Best Paper Award at the 1996 IEEE International ASIC Conference, and nominations for Best Paper Awards at the 2007 IEEE/ACM Design Automation Conference (DAC) and the 2008 IEEE/ACM International Conference on Computer-Aided Design (ICCAD). One of his publications was recognized in the 2013 IEEE/ACM Design Automation Conference (DAC) as one of the "Top 10 Cited Papers in 50 Years of DAC". He received a Ph.D. in Electrical Engineering from Rensselaer Polytechnic Institute, Troy, New York. He is a Fellow of the IEEE.

#### **T8: Analog Techniques for Nano-power Circuits**

This tutorial presents the design methodology and examples of analog circuits having nanoampere consumption with application in systems with short activity periods followed long standby. They are essential for the area of energy harvesting where the amount of available energy can unpredictably change by orders of magnitude. Low load efficiency of power management becomes a very important parameter in a wide breadth of applications. Circuit examples include biasing, precision voltage references, oscillators, charge pumps, adaptive speed amplifiers and comparators, LDOs, DCDC converters.

#### Instructor: Vadim Ivanov

Vadim Ivanov received the MSEE and the Ph.D. in 1980 and 1987, respectively, both in the USSR. He designed electronic systems and ASICs for naval navigation equipment from 1980 to 1991 in St. Petersburg, Russia, and mixed-signal ASICs for sensors, GPS/GLONASS receivers and for motor control between 1991 and 1995. He joined Burr Brown (presently Texas Instruments, Tucson) in 1996 as a senior member of technical staff, where he has been involved in the design of the operational, instrumentation, power amplifiers, references, and switching and linear voltage regulators. He has over 80 US patents and applications on analog circuit techniques and authored over 30 technical papers and three books: "Power Integrated Amplifiers" (Leningrad, Rumb, 1987), "Analog system design using ASICs" (Leningrad, Rumb, 1988), both in Russian, and " Operational Amplifier Speed and Accuracy Improvement", Kluwer, 2004.

#### **T9: Frequency Synthesizers for Wireless Transceivers**

A frequency synthesizer is a key building block in wireless systems. The  $\Delta\Sigma$  fractional-N PLLbased synthesizer plays a critical role in modern transceivers not only as a local oscillator but also as a phase modulator with direct digital modulation. However, the traditional PLL in advanced CMOS technology suffers from poor scalability, loop parameter variability, leakage current and linearity problems. Accordingly, diversified PLL architectures and circuit techniques have been recently proposed in consideration of performance, power and cost, thus making it more difficult than ever for circuit designers to choose the right design solution. This tutorial gives some insight into PLL basics tailored for circuit designers. Then, system perspectives and practical circuit design aspects for frequency synthesis will be presented.

#### Instructor: Woogeun Rhee

Woogeun Rhee is a Professor at Tsinghua University, China. He received the B.S. degree from Seoul National University in 1991, the M.S. degree from UCLA in 1993, and the Ph.D. degree from the University of Illinois, Urbana-Champaign, in 2001. From 1997 to 2001, he was with Conexant Systems, CA, where he was a Principal Engineer and developed low-power low-cost fractional-N synthesizers. From 2001 to 2006, he was with IBM Thomas J. Watson Research Center, NY and worked on clocking area for high-speed I/O serial links. In August 2006, he joined the faculty of Tsinghua University, China. He currently holds 19 U.S. patents.

#### T10: CMOS Sensors for 3D Imaging

3D imaging has become a hot research topic in the last few years, driven by the needs of emerging markets looking for next-generation user interfaces based on gesture control. Moreover, 3D vision systems offer amazing possibilities of improvement in many other areas like automotive, security and surveillance, cultural heritage preservation, ambient-assisted living, industrial control, etc., because they significantly increase the robustness of object classification with respect to conventional 2D imagers. This tutorial will introduce participants to the exciting field of 3D imaging, providing an overview about image-sensor architectures capable of distance measurement. An introduction to existing 3D imaging technologies will be given, addressing the peculiarities of each measuring technique and the possible application domains. The focus is on solid-state sensor architectures as enabling technologies to improve the performance of 3D vision systems, with a particular emphasis on time-of-flight implementations. Finally, participants will get some practical tools such as figure of merits and experimental characterizations guidelines for a comprehensive comparison of 3D imager performance and a perspective toward the future challenges in this fast-evolving field.

#### Instructor: David Stoppa

David Stoppa received the Ph.D. degree in Microelectronics from the University of Trento, Italy. He is the head of the Integrated Radiation and Image Sensors research unit at FBK where he has been working as a research scientist since 2002 and as group leader of the Smart Optical Sensors and Interfaces group from 2010 to 2013. His research interests are in the field of CMOS image sensors and biosensors. He has published more than 100 papers, and holds several patents in the field of image sensors. He is currently a member of the ISSCC ITPC and was technical committee member of 'International Image Sensors Workshop' in 2009 and 2013. Dr. Stoppa received the 2006 ESSCIRC Best Paper Award.

## FORUM 1

### Sunday February 22<sup>nd</sup>, 8:00 AM

## F1: High-Speed Interleaved ADCs

| Organizer:    | Stéphane Le Tual, STmicroelectronics, Crolles, France                                             |

|---------------|---------------------------------------------------------------------------------------------------|

| Co-organizer: | Borivoje Nikolic, University of California, Berkeley, CA                                          |

| Committee:    | <b>Tetsuya lizuka,</b> University of Tokyo, Tokyo, Japan<br>Ichiro Fujimori, Broadcom, Irvine, CA |

Time-interleaved ADCs have become critical components in high-speed wireline and wireless communication systems. This forum will deliver a comprehensive treatment of state-of-the art design techniques for high-speed interleaved ADCs. Topics include transistor-level design techniques, calibration (estimation & correction), as well as the link between system specifications and required ADC performance.

|                        | Agenda                                                                                                                                             |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>Time</u><br>8:00 AM | <u>Topic</u><br>Breakfast                                                                                                                          |

| 8:20 AM                | Introduction by Chair                                                                                                                              |

| 8:30 AM                | Interleaved ADCs Through the Ages<br>Ken Poulton, Keysight Laboratories, Santa Clara, CA                                                           |

| 9:20 AM                | Mismatch Error Correction for High-Resolution,<br>GS/s time-Interleaved ADCs<br><i>Per Löwenborg,</i> Signal Processing Devices, Linköping, Sweden |

| 10:10 AM               | Break                                                                                                                                              |

| 10:35 AM               | Highly Accurate Adaptive Digital Calibration for High-Speed<br>High-Resolution Time-Interleaved ADCs<br>Takashi Oshima, Hitachi, Tokyo, Japan      |

| 11:25 AM               | ADC Interleaving Errors Corrected by Adaptive Post-Processing<br>Asad Abidi, University of California, Los Angeles, CA                             |

| 12:15 PM               | Lunch                                                                                                                                              |

| 1:20 PM                | Specifications vs. Applications: Driving Architectural Choices<br>Aaron Buchwald, Entropic, Irvine, CA                                             |

| 2:10 PM                | GS/s Time-Interleaved ADCs for Broadband Multi-Carrier<br>Signal Reception<br>Kostas Doris, NXP, Eindhoven, The Netherlands                        |

| 3:00 PM                | Break                                                                                                                                              |

| 3:20 PM                | Embedded CMOS ADCs for Optical Communications<br>Yuriy M. Greshishchev, Ciena, Ottawa, Canada                                                      |

| 4:10 PM                | Panel<br>Moderators: <i>Bora Nikolic (UC Berkeley)</i><br><i>Dave Robertson (ADI)</i>                                                              |

| 5:00 PM                | Closing remarks by Chair                                                                                                                           |

|                        |                                                                                                                                                    |

### F2: Memory Trends: From Big Data to Wearable Devices

| Organizer: | Jonathan Ch | ang, TSMC, | Hsinchu, | Taiwan |

|------------|-------------|------------|----------|--------|

|------------|-------------|------------|----------|--------|

Committee: Jonathan Chang, TSMC, Hsinchu, Taiwan Leland Chang, IBM, Yorktown Heights, NY Antoine Dupret, CEA Leti-LIST, Gif-sur-Yvette, France Chulwoo Kim, Korea University, Seoul, Korea Fatih Hamzaoglu, Intel, Hillsboro, OR Takefumi Yoshikawa, Panasonic, Kyoto, Japan

Memory continues to be a critical element in the full range of VLSI applications - from big data to mobile applications to wearable devices. Recent trends, including process technology scaling limits, new memory applications, and evolving high-performance and low-power requirements, have driven the development of emerging memories. As both discrete and embedded memory scaling becomes ever more challenging, there is a widespread effort to look for alternative memory technologies to replace the entrenched SRAM, DRAM, or Flash. This forum will bring together systems designers to discuss memory needs for future applications and memory designers to describe the latest developments in emerging and next generation memories.

| <u>Topic</u><br>Breakfast                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Introduction                                                                                                                                                   |

| Memory Requirement Trends and Challenges: Servers to Devices<br>Suresh Chittor, Intel, Hillsboro, OR                                                           |

| Memory System Requirements for the Big-Data Application<br>Data-Centric Computing<br>Ken Takeuchi, Chuo University, Tokyo, Japan                               |

| Break                                                                                                                                                          |

| Memory and Storage Requirement and Trend for ChromeOS<br>Eric Shiu, Google, Mountain View, CA                                                                  |

| Emerging Memories in Embedded Systems: Opportunities for the<br>Digital Architect, Challenges for the Designers<br>Fabien Clermidy, CEA-Leti, Grenoble, France |

| Lunch                                                                                                                                                          |

| 3D NAND Flash: from Enterprise to Embedded Storages<br>Ki-Tae Park, Samsung, Hwasung, Korea                                                                    |

| Addressing Future Memory Challenges with Device Abstraction<br>J. Thomas Pawlowski, Micron, Boise, ID                                                          |

| Break                                                                                                                                                          |

| Technology Trends and Applications of MRAM<br>from Big Data to Wearable Devices<br>Shinobu Fujita, Toshiba, Kawasaki, Japan                                    |

| RRAM for Data Abundant System Technology:<br>Managing Expectations and Minimizing Disappointments<br>Malgorzata Jurczak, IMEC, Leuven, Belgium                 |

| Conclusion                                                                                                                                                     |

|                                                                                                                                                                |

## ES1: STUDENT RESEARCH PREVIEW (SRP)

The Student Research Preview (SRP) will highlight selected student research projects in progress. The SRP consists of 25 one-minute presentations followed by a Poster Session, by graduate students from around the world, which have been selected on the basis of a short submission concerning their on-going research. Selection is based on the technical quality and innovation of the work. This year, the SRP will be presented in three theme sections: Low-Power Data Converters and High-Speed Links; Biomedical Circuits and Systems; and Energy-Efficient Circuits for Sensors, RF, and Platform.

The Student Research Preview will begin with a brief talk by a distinguished member of the solid-state circuit community, Professor Emerita Lynn Conway of the University of Michigan, Ann Arbor.

Her remarks are scheduled for Sunday, February 22<sup>nd</sup>, starting at 7:30 pm. SRP is open to all ISSCC registrants.

| Chair:              | Jan Van der Spiegel | University of Pennsylvania, USA     |

|---------------------|---------------------|-------------------------------------|

| Co-Chair:           | SeongHwan Cho       | KAIST, Korea                        |

| Co-Chair:           | Marian Verhelst     | Kath. University of Leuven, Belgium |

| Secretary:          | SeongHwan Cho       | KAIST, Korea                        |

| Advisor:            | Kenneth C. Smith    | University of Toronto, Canada       |

| Media/Publications: | Laura Fujino        | University of Toronto, Canada       |

| A/V:                | John Trnka          | Rochester, MN                       |

|                     |                     |                                     |

### **COMMITTEE MEMBERS**

Brvan Ackland, Stevens Institute of Technology, USA Andrea Baschirotto, University of Milan-Bicocca, Italy William Bowhill, Intel, USA SeongHwan Cho, KAIST, Korea Denis Daly, Maxim Integrated, USA Andreas Demosthenous, University College London, UK Vincent Gaudet, University of Waterloo, Canada Manish Goel, Samsung Electronics, USA Chun-Huat Heng, National University of Singapore, Singapore Makoto Ikeda, University of Tokyo, Japan Jaeha Kim, Seoul National University, Korea Tsung-Hsien Lin, National Taiwan University, Taiwan Dejan Marković, University of California, Los Angeles, USA Akira Matsuzawa, Tokyo Institute of Technology, Japan Shahriar Mirabbasi, University of British Columbia, Canada Tinoosh Mohsenin, University of Maryland, USA Nils Pohl, Ruhr-University Bochum, Germany Patrick Reynaert, University of Leuven, Belgium Bing Sheu, TSMC, Taiwan Sameer Sonkusale, Tufts University, USA Jan Van der Spiegel, University of Pennsylvania, USA Marian Verhelst. University of Leuven. Belgium Jeffrey Weldon, Carnegie Mellon University. USA GuoXing Wang, Shanghai Jiao Tong University, China Peter (Chung-Yu) Wu, National Chiao Tung University, Taiwan

**EVENING SESSION**

Sunday February 22<sup>nd</sup>, 8:00 PM

## ES2: Brain-Machine Interfaces: Integrated Circuits Talking to Neurons

Organizer:

Firat Yazicioglu, IMEC, Leuven, Belgium Peng Cong, Google, Mountain View, CA Shahriar Mirabbasi, University of British Columbia, Vancouver, Canada

Chair:

Peng Cong, Google, Mountain View, CA Shahriar Mirabbasi, University of British Columbia, Vancouver, Canada

We have not unlocked the three pounds of matter sitting in between our ears. -Barack Obama

The brain is the most complex human organ, with energy efficiency far beyond that of any existing equivalent computing technology. Great efforts are being invested globally into deciphering its functioning. If successful, the resulting knowledge may forever change medical, consumer, and communications semiconductor industry sectors. A first significant challenge on the road towards this goal is the creation of instruments, generally enabled by integrated circuits, which can interact with a large number of the brain neurons and interpret such interactions.

This evening session will discuss technologies and circuit design solutions for connecting integrated circuits to neural circuits and will explore future application opportunities for such brain-machine interfaces. Experts in related technologies, circuit design, and applications from three continents will present an entertaining session on the impact of semiconductor technologies on medical applications and human-machine interaction.

| <u>Time</u><br>8:00 PM | <u>Topic</u><br>Neural Interfacing: Challenges and Opportunities for Circuit Designers<br><i>Tim Denison, Medtronic, Minneapolis, MN</i> |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 8:25 PM                | CMOS Technology to Interface with Single Neurons and Axons<br>Andreas Hierlemann, ETHZ, Zurich, Switzerland                              |

| 8:50 PM                | Circuits and Systems for Implantable Brain Monitoring<br>Jan Rabaey, University of California, Berkeley, CA                              |

| 9:15 PM                | Neural Stimulation and Closed-Loop Prosthetics<br>Minkyu Je, Daegu Gyeongbuk Institute of Science & Technology,<br>Daegu, Korea          |

| 9:40 PM                | Panel Discussions                                                                                                                        |

## Plenary Session — Invited Papers

Chair: Anantha Chandrakasan, Massachusetts Institute of Technology, Cambridge, MA ISSCC Conference Chair

Associate Chair: Hoi-Jun Yoo, KAIST, Daejeon, Korea ISSCC Program Committee Chair

#### FORMAL OPENING OF THE CONFERENCE

8:30 AM

1.1

Silicon Technologies and Solutions for the Data-Driven World Kinam Kim, President, Samsung Electronics, Kiheung, Korea

8:45 AM

Silicon technology has been the core driver of the modern information revolution, forming the foundation on which electronics devices have been built. Advances in silicon-scaling technology have placed general-purpose computing in the palm of one's hand! Despite concerns for the demise of scaling, higher performance in electronic systems for the coming decades is expected, thanks to innovations in materials, structures, and processes. Performance-enhancing technologies, such as TSVs and 3D ICs, will drive the evolution of the fast-expanding data-driven world. As usual, these technological advances will breed new applications and new fields (Internet of Things, mobile healthcare, and others), all of which will catalyze explosive data growth. Both silicon and silicon-system technologies will need to evolve in order to conform to the future data-driven world. Future system-technology directions from the perspectives of servers, clients, and connectivity will also be discussed. Finally, issues associated with this data explosion (such as data security) will be presented.

#### ISSCC, SSCS, IEEE AWARD PRESENTATIONS 9:25 AM

#### BREAK

#### 1.2 The Future of IC Design Innovation Sehat Sutardja, Chairman and CEO, Marvell Technology Group, Santa Clara, CA

One of the greatest achievements of humankind is undoubtedly our ability to build tiny machines that marry the functionalities of computers and wireless communication devices so cheaply that almost anyone in the world can afford them. Every one of us has at least one such device in our pocket, yet we rarely think about how in the world anyone could have created such a thing! Even the experts in our industry could not have predicted that this would have happened so soon. What we have achieved could be considered nothing short of a miracle, considering that billions of transistors have to work together flawlessly. (Well, sort of.) The reality is that some of these devices are now so complex that we need thousands of engineers for design, validation, and support, which inevitably causes inefficiencies and bugs. Sadly, the way we build these devices has not changed much over the past decades. Integrated-circuit design engineers blindly do what they are told to - integrate as much functionality into a single device, believing that more is better! This more- the-better mentality is not surprising because we saw in the past that the more we integrate, the cheaper things would become. Unfortunately, times have changed. The cost and complexity of building billions of transistors on a single device is finally taking a toll on our engineers. If chip-design engineers had also looked at the financial optimization of the overall design process, they would have built things differently. They should have realized that certain functions are better grouped into highly specialized integrated circuits that could easily and seamlessly talk to each other without compromising the overall system cost. The key to making this happen is what I call the Lego-Block approach of designing integrated circuits. However, in order for the Lego-Block approach to materialize, we need to change the way we architect our devices.

9:55 AM

10:10 AM

## Monday February 23<sup>rd</sup>, 10:50 AM

We need to do many things: Define a new chip-to-chip interconnect protocol; take advantage of multi-chip-module packaging and high-speed SerDes technology; redefine the memory hierarchy to take advantage of 3D solid-state memory instead of blindly increasing the DRAM size in our devices; repartition DRAM to serve different logical functions instead of building gigantic single-die DRAM to serve every function; change the way we build DRAMs so that they are optimized more for performance and power efficiency instead of capacity; and redefine what should be done in hardware versus software. In short, we need to change our way of thinking, and be brave enough to reject common wisdom. If we fail to take action, soon we will no longer see cost savings. On the other hand, if we succeed, we will see life beyond the end of Moore's Law!

#### 1.3 Analog CMOS from 5 Micrometer to 5 Nanometer Willy Sansen, Professor Emeritus, Katholieke Universiteit Leuven, Leuven, Belgium 10:50 AM

Since the early years of analog design in CMOS, expertise has been focused on building blocks, with emphasis on trade-offs among speed, noise, and power consumption. But, present application systems (such as mobile SoC, Internet-of-Things, automotive, biomedical, FPGA interfaces), all require mixed-signal design and digitally-assisted analog. "How much analog has to be combined with how much digital?" is an open question.

This presentation will look back briefly through the history of CMOS analog design and give a projection on how analog may look in future Nanometer CMOS. In these new technologies, the supply voltage keeps on shrinking, making offset and 1/f noise even more important than before.

Nowadays, analog techniques all aim at the cancellation of resistances, to save power. They also try to cancel capacitances, to enhance speed. As well, cancellation of noise and distortion have become commonplace. Such cancellation techniques will be reviewed and compared. In parallel, several technologies such as FinFETs and FD-SOI, are in competition for future Nanometer design. Below gate lengths of 10nm, materials other than Silicon, such as Germanium, need to be considered. Also Nanowires and Nanotubes have become viable candidates for Nanometer Analog.

| PRESENTATION TO PLENARY SPEAKERS | 11:30 AM |

|----------------------------------|----------|

|----------------------------------|----------|

#### CONCLUSION

11:35 AM

## RF TX/RX Design Techniques

|      | Session Chair:<br>Associate Chair:                                                                                                | Ehsan Afshari, Cornell University, Ithaca, NY<br>Minoru Fujishima, Hiroshima University, Hiroshima,                                                                                                                  | Japan   |

|------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 2.1  | and Thermal-Noise<br>H. Wu <sup>1,2</sup> , M. Mikhema                                                                            | uctorless Wideband Receiver with Phase-<br>Cancellation<br>ar <sup>2</sup> , D. Murphy <sup>2</sup> , H. Darabi <sup>2</sup> , M-C. F. Chang <sup>1</sup><br>iia, Los Angeles, CA; <sup>2</sup> Broadcom, Irvine, CA | 1:30 PM |

| 2.2  | <b>in 0.18µm SOI CMO</b><br>B. van Liempd <sup>1</sup> , B. He<br>U. Karthaus <sup>3</sup> , K-F. Bin                             | prshberg¹, K. Raczkowski¹, S. Ariumi²,<br>k³, J. Craninckx¹<br>m; ²Murata, Kyoto, Japan                                                                                                                              | 2:00 PM |

| 2.3  | <b>23.7dB Isolation in</b><br><i>F. Meng<sup>1</sup>, K. Ma<sup>1</sup>, K. S</i><br><sup>1</sup> Nanyang Technologia             |                                                                                                                                                                                                                      | 2:15 PM |

| 2.4  | with Double-RF N-F<br>and 1.5-to-2.9dB N<br>Z. Lin <sup>1</sup> , P-I. Mak <sup>1</sup> , R.<br><sup>1</sup> University of Macau, | P. Martins <sup>1,2</sup>                                                                                                                                                                                            | 2:30 PM |

| 2.5  | CMOS Supporting 2<br>W. Ye <sup>1</sup> , K. Ma <sup>1</sup> , K. S.<br><sup>1</sup> Nanyang Technologie                          |                                                                                                                                                                                                                      | 2:45 PM |

|      | Break                                                                                                                             |                                                                                                                                                                                                                      | 3:00 PM |

| 2.6  | CMOS for WCDMA/<br>A. F. Aref, R. Negra, N                                                                                        |                                                                                                                                                                                                                      | 3:15 PM |

| 2.7  | Range Achieving a<br>S-C. Lee, J-S. Paek, J                                                                                       | dulator with 10dB ET Operation Dynamic<br>PAE of 42.6% at 27.0dBm PA Output Power<br>I-H. Jung, Y-S. Youn, S-J. Lee, M-S. Cho, J-J. Han,<br>T. Nomiyama, S-H. Lee, I-Y. Sohn, T. B. Cho,<br>, Hwaseong, Korea        | 3:45 PM |

| 2.8  | Class-G Doherty Eff<br>S. Hu <sup>1</sup> , S. Kousai <sup>2</sup> , H.                                                           | <b>Digital Power Amplifier with Hybrid</b><br>i <b>ciency Enhancement</b><br><i>Wang<sup>1</sup></i><br>ēchnology, Atlanta, GA; <sup>2</sup> Toshiba, Kawasaki, Japan                                                | 4:15 PM |

| 2.9  | with Dynamic Load                                                                                                                 | <b>ak PAE mm-Wave Digital Power Amplifier<br/>Modulation</b><br>University of Southern California, Los Angeles, CA                                                                                                   | 4:45 PM |

| 2.10 | Amplifier with 21%                                                                                                                | ux, Talence, France                                                                                                                                                                                                  | 5:00 PM |

|      | Conclusion                                                                                                                        |                                                                                                                                                                                                                      | 5:15 PM |

## Ultra-High-Speed Wireline Transceivers and Energy-Efficient Links

|            |                                                                                                                                                     | <b>Ken Chang,</b> Xilinx, San Jose, CA<br><b>Shunichi Kaeriyama,</b> Renesas, Tokyo, Japan                                                                                  |         |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 3.1        | for Backplane App                                                                                                                                   |                                                                                                                                                                             | 1:30 PM |

| 3.2        | Signal Conditioner<br>DFE and Data-Rat<br>T. Kawamoto <sup>1</sup> , T. No<br>M. Tsuge <sup>2</sup> , T. Usugi<br>T. Kawamata <sup>2</sup> , Y. Ito |                                                                                                                                                                             | 2:00 PM |

| 3.3<br>DS1 | Transceiver in 20<br>P. Upadhyaya, J. Sa                                                                                                            | woj, F-T. An, A. Bekele, A. Jose, B. Xu,<br>. Aslanzadeh, H. Hedayati, J. Im, S-W. Lim,<br>Y. Frans, K. Chang                                                               | 2:30 PM |

|            | Break                                                                                                                                               |                                                                                                                                                                             | 3:00 PM |

| 3.4        | in 28nm CMOS                                                                                                                                        |                                                                                                                                                                             | 3:15 PM |

| 3.5        | Transmitter in 14                                                                                                                                   | ty, A. Elshazly, Y-Y. Huang, H. Song,                                                                                                                                       | 3:45 PM |

| 3.6        | FFE and Dynamic<br>A. Shafik, E. Zhian                                                                                                              | ADC-Based Receiver with Embedded 3-Tap Analog<br>ally-Enabled Digital Equalization in 65nm CMOS<br>Tabasy, S. Cai, K. Lee, S. Hoyos, S. Palermo<br>ity, College Station, TX | 4:00 PM |

| 3.7        | with 20ns Power-<br>Energy-Proportion                                                                                                               |                                                                                                                                                                             | 4:15 PM |

| 3.8        | Transceiver Using                                                                                                                                   |                                                                                                                                                                             | 4:45 PM |

#### Conclusion

5:15 PM

## Processors

|            |                                                                                                                                                                                                                                                                                                                                                                                                | Atsuki Inoue, Fujitsu, Kawasaki, Japan<br>Luke (Jinuk) Shin, Oracle, Redwood Shores, CA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 4.1        | J. Warnock <sup>1</sup> , B. Cur<br>S. Carey <sup>2</sup> , G. Salem<br>M. Wood <sup>2</sup> , Y-H. Cha<br>L. Sigal <sup>7</sup> , R. Nigagli<br>G. Strevig <sup>3</sup> , D. Drep<br><sup>1</sup> IBM Systems and T<br><sup>3</sup> IBM Systems and T<br><sup>3</sup> IBM Systems and T<br><sup>6</sup> IBM Systems and T<br><sup>6</sup> IBM Systems and T<br><sup>7</sup> IBM Research, Yor | ation IBM System z Microprocessor<br>ran <sup>2</sup> , J. Badar <sup>3</sup> , G. Fredeman <sup>2</sup> , D. Plass <sup>2</sup> , Y. Chan <sup>2</sup> ,<br><sup>4</sup> , F. Schroeder <sup>5</sup> , F. Malgioglio <sup>2</sup> , G. Mayer <sup>5</sup> , C. Berry <sup>2</sup> ,<br>nn <sup>2</sup> , M. Mayo <sup>2</sup> , J. Isakson <sup>3</sup> , C. Nagarajan <sup>6</sup> , T. Werner <sup>5</sup> ,<br>oni <sup>3</sup> , M. Cichanowski <sup>3</sup> , J. Zitz <sup>8</sup> , M. Ziegler <sup>7</sup> , T. Bronson <sup>3</sup> ,<br>s <sup>3</sup> , R. Puri <sup>7</sup> , D. Malone <sup>2</sup> , D. Wendel <sup>5</sup> , P-K. Mak <sup>2</sup> , M. Blake <sup>2</sup><br>Fechnology, Yorktown Heights, NY<br>Fechnology, Poughkeepsie, NY<br>Fechnology, Williston, VT<br>Fechnology, Boeblingen, Germany<br>Fechnology, Bangalore, India<br>ktown Heights, NY<br>Fechnology, Hopewell Junction, NY | 1:30 PM |

| 4.2        | P. Li, J. L. Shin, G. I<br>H. Cho, S. Dash, R.                                                                                                                                                                                                                                                                                                                                                 | <b>4MB L3 Cache SPARC M7 Processor</b><br>Konstadinidis, F. Schumacher, V. Krishnaswamy,<br>Masleid, C. Zheng, Y. D. Lin, P. Loewenstein,<br>an, D. Huang, C. Hwang, W. Hsu, C. McAllister<br>tores, CA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2:00 PM |

| 4.3        | SPARC M7 Proces<br>V. Krishnaswamy, J.                                                                                                                                                                                                                                                                                                                                                         | Brooks, G. Konstadinidis, C. McAllister,<br>Is, J. L. Shin, Y. YangGong, H. Zhang                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2:30 PM |

| 4.4<br>DS1 | 188K-CoreMark 28<br>Applications with<br>R. Luijten <sup>1</sup> , D. Phan                                                                                                                                                                                                                                                                                                                     | licroserver Based on a 12-Core 1.8GHz<br>Bam Bulk CMOS 64b SoC for Big-Data<br>159GB/s/L Memory Bandwidth System Density<br>R <sup>2</sup> , R. Clauberg <sup>1</sup> , M. Cossale <sup>1</sup> , H. N. Nguyen <sup>2</sup> , M. Pandya <sup>2</sup><br>cchlikon, Switzerland<br>ductor, Austin, TX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2:45 PM |

|            | Break                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3:00 PM |

| 4.5<br>DS1 | B. Bowhill <sup>1</sup> , B. Stack<br>C. Morganti <sup>2</sup> , C. Hou<br>J. Crop <sup>2</sup> , D. Bradley                                                                                                                                                                                                                                                                                   | ssor E5-2600 v3: A 22nm 18-Core Product Family<br>khouse <sup>2</sup> , N. Nassif <sup>1</sup> , Z. Yang <sup>1</sup> , A. Raghavan <sup>1</sup> ,<br>ughton <sup>1</sup> , D. Krueger <sup>2</sup> , O. Franza <sup>1</sup> , J. Desai <sup>2</sup> ,<br><sup>2</sup> , C. Bostak <sup>2</sup> , S. Bhimji <sup>1</sup> , M. Becker <sup>1</sup><br><sup>2</sup> Intel, Fort Collins, CO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3:15 PM |

| 4.6        | with Tetra-Paralle                                                                                                                                                                                                                                                                                                                                                                             | alable Deep Learning/Inference Processor<br>I MIMD Architecture for Big-Data Applications<br>Shin, J. Lee, S. Choi, H-J. Yoo, KAIST, Daejeon, Korea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3:45 PM |

| 4.7        | 22nm Tri-Gate CM<br>Detection for Tole<br>Temperature and                                                                                                                                                                                                                                                                                                                                      | aptive and Resilient Domino Register File in<br>OS Featuring In-Situ Timing Margin and Error<br>rance to Within-Die Variation, Voltage Droop,<br>Aging<br>kunaga, P. Aseron, T. Nguyen Jr, C. Augustine,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4:15 PM |

| 4.8<br>DS1 | <i>K. Wilcox</i> <sup>1</sup> , <i>D. Akese</i><br><i>G. Krishnan</i> <sup>1</sup> , <i>H. Mc</i><br><i>S. Sundaram</i> <sup>4</sup> , <i>J. W</i><br><sup>1</sup> AMD, Boxborough,                                                                                                                                                                                                            | Dptimized for Power and Area Efficiency<br>on <sup>1</sup> , H. R. Fair III <sup>1</sup> , J. Farrell <sup>1</sup> , D. Johnson <sup>2</sup> ,<br>Intyre <sup>3</sup> , E. McLellan <sup>1</sup> , S. Naffziger <sup>2</sup> , R. Schreiber <sup>4</sup> ,<br>hite <sup>1</sup><br>MA; <sup>2</sup> AMD, Fort Collins, CO<br>A; <sup>4</sup> AMD, Austin, TX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4:45 PM |

|            | Conclusion                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5:15 PM |

## Monday February 23rd, 1:30 PM

|      | Session Chair:<br>Associate Chair:                                                                                                                  |                                                                                                                                                                                                                                   |         |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|      |                                                                                                                                                     | Enschede, The Netherlands                                                                                                                                                                                                         |         |

| 5.1  | Interleaved Clock                                                                                                                                   | Ind Chopper Operational Amplifier with 800kHz<br>s and Input Bias-Current Trimming<br>Devices, San Jose, CA                                                                                                                       | 1:30 PM |

| 5.2  | 8µV Offset for Cur<br>L. Xu <sup>1</sup> , B. Gönen <sup>1</sup> , C<br><sup>1</sup> Delft University of                                            | C with ±30V Input Common-Mode Range and<br>rrent Sensing Applications<br>2. Fan <sup>2</sup> , J. H. Huijsing <sup>1</sup> , K. A. Makinwa <sup>1</sup><br>Technology, Delft, The Netherlands<br>Products, Delft, The Netherlands | 2:00 PM |

| 5.3  | Orthogonal Frequ<br>Y-L. Tsai, F-W. Lee,                                                                                                            | 2dB Crosstalk 0.061mm <sup>2</sup> CCIA with an<br>ency Chopping Technique<br><i>T-Y. Chen, T-H. Lin</i><br>iversity, Taipei, Taiwan                                                                                              | 2:30 PM |

| 5.4  | Supply for Ultra-L                                                                                                                                  | Reference Voltage Operational from 0.5V<br>.ow Power Systems<br>Craig, N. E. Roberts, D. D. Wentzloff, B. H. Calhoun<br>ville, VA                                                                                                 | 2:45 PM |

|      | Break                                                                                                                                               |                                                                                                                                                                                                                                   | 3:00 PM |

| 5.5  | <b>in 28nm UTBB FD</b><br>J. Lechevallier <sup>1,2</sup> , R<br>E. Klumperink <sup>1</sup> , B.                                                     | te, Enschede, The Netherlands                                                                                                                                                                                                     | 3:15 PM |

| 5.6  | Control and Redu<br>Range<br>S. B. Nasir, S. Gang                                                                                                   | igital Low-Dropout Regulator with Adaptive<br>ced Dynamic Stability for Ultra-Wide Dynamic<br>gopadhyay, A. Raychowdhury<br>Technology, Atlanta, GA                                                                               | 3:45 PM |

| 5.7  | J. M. Lee <sup>1</sup> , Y. Ji <sup>1</sup> , S.<br>H-J. Park <sup>1</sup> , J-Y. Sin<br><sup>1</sup> Pohang University                             | <b>Reference Circuit</b><br>. <i>Choi', Y-C. Cho<sup>2</sup>, S-J. Jang<sup>2</sup>, J. S. Choi<sup>2</sup>, B. Kim<sup>1</sup>,</i><br><sup>1</sup><br>of Science and Technology, Pohang, Korea<br>ics, Hwaseong, Korea          | 4:15 PM |

| 5.8  | Voltage Reference<br>Fuel-Gauge Appli<br>G. Maderbacher, S.                                                                                         | Marsili, M. Motz, T. Jackum, J. Thielmann,<br>ruber, F. Hus, C. Sandner                                                                                                                                                           | 4:30 PM |

| 5.9  | D. Griffith <sup>1</sup> , J. Murd                                                                                                                  | <b>de Crystal Oscillator for Single-Crystal Radios</b><br><i>lock', P. T. Røine<sup>e</sup>, T. Murphy<sup>1</sup></i><br>, Dallas, TX; <sup>2</sup> Texas Instruments, Oslo, Norway                                              | 4:45 PM |

| 5.10 | <b>Oscillator with –2</b><br>J. Lee <sup>1</sup> , P. Park <sup>1</sup> , S.<br><sup>1</sup> Institute of Microe<br><sup>2</sup> KAIST, Daejeon, Ke | lectronics, Singapore, Singapore                                                                                                                                                                                                  | 5:00 PM |

|      | Conclusion                                                                                                                                          |                                                                                                                                                                                                                                   | 5:15 PM |

## Monday February 23<sup>rd</sup>, 1:30 PM

## Image Sensors and Displays

|            | Session Chair:<br>Associate Chair:                                                                                                                     | <b>Yusuke Oike,</b> Sony, Atsugi, Japan<br><b>Young-Sun Na,</b> LG Electronics, Seoul, Korea                                                                                                                                                                                  |         |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 6.1        | Sensor for New Im<br>A. Suzuki <sup>1</sup> , N. Shima<br>K. Koiso <sup>2</sup> , A. Masaga                                                            | or, Kikuyou, Japan<br>lapan<br>ukuoka, Japan                                                                                                                                                                                                                                  | 1:30 PM |

| 6.2        | High-Speed Colun<br>R. Funatsu <sup>1</sup> , S. Huai<br>D. Estrada <sup>2</sup> , S. Yan <sup>2</sup> ,<br>H. Shimamoto <sup>1</sup> , B. I           | hnology Research Laboratories, Tokyo, Japan                                                                                                                                                                                                                                   | 2:00 PM |