# 2011 PRESS KIT

#### **ISSCC PRESS KIT DISCLAIMER**

The material presented here is preliminary. As of November 1, 2010, there is not enough information to guarantee its correctness. Thus, it must be used with some caution.

## ISSCC VISION STATEMENT

The International Solid-State Circuits Conference is the foremost global forum for presentation of advances in solid-state circuits and systems-on-a-chip. The Conference offers a unique opportunity for engineers working at the cutting edge of IC design and use to maintain technical currency, and to network with leading experts.

## TABLE OF CONTENTS

| ISSCC 2011 – CONFERENCE OVERVIEW                 |    |

|--------------------------------------------------|----|

| CONFERENCE THEME                                 |    |

| EVENTS                                           |    |

| PAPER STATISTICS                                 | 5  |

| PLENARY SESSION                                  | 6  |

| TECHNICAL HIGHLIGHTS                             | 9  |

| EDUCATIONAL EVENTS                               |    |

| EVENING SESSIONS                                 |    |

| SUBCOMMITTEE CONTRIBUTIONS                       |    |

| ISSCC 2011 – ANALOG                              |    |

| OVERVIEW                                         |    |

| TREND ESSAY                                      |    |

| ISSCC 2011 – DATA CONVERTERS                     | 23 |

| OVERVIEW                                         |    |

|                                                  | 07 |

| ISSCC 2011 – ENERGY-EFFICIENT DIGITAL            |    |

| OVERVIEW                                         |    |

| ISSCC 2011 – HIGH-PERFORMANCE DIGITAL            |    |

| OVERVIEW                                         |    |

| TREND ESSAY                                      |    |

| TREND CHARTS                                     |    |

| ISSCC 2011 – IMAGERS, MEMS, MEDICAL AND DISPLAYS | 30 |

| OVERVIEW                                         |    |

| TREND ESSAYS                                     |    |

|                                                  |    |

| ISSCC 2011 – MEMORY                              |    |

| OVERVIEW                                         | -  |

| TREND ESSAY                                      | 51 |

| ISSCC 2011 – RADIO FREQUENCY                     |    |

| OVERVIEW                                         |    |

| TREND ESSAY                                      |    |

|                                                  | •  |

| ISSCC 2011 – TECHNOLOGY DIRECTIONS               |    |

| OVERVIEW                                         |    |

| TREND ESSAY                                      | 67 |

| ISSCC 2011 – WIRELESS                            | 63 |

| OVERVIEW                                         |    |

|                                                  |    |

| ISSCC 2011 – WIRELINE                            | 73 |

| OVERVIEW                                         |    |

| TREND ESSAY                                      |    |

| ISSCC 2011 – SESSION OVERVIEW MATERIALS |  |

|-----------------------------------------|--|

| CONDITIONS OF PUBLICATION.              |  |

| SESSION OVERVIEWS                       |  |

| ISSCC 2011 – PRESS COPY MATERIALS       |  |

| CONDITIONS OF PUBLICATION               |  |

| TABLE OF FEATURED PAPERS                |  |

| PRESS COPY                              |  |

| ISSCC 2011 – CONTACT INFORMATION        |  |

| TECHNICAL EXPERTS                       |  |

| GENERAL CONTACTS                        |  |

|                                         |  |

## ISSCC 2011 Conference Overview

© COPYRIGHT 2011 ISSCC-DO NOT REPRODUCE WITHOUT PERMISSION

### **CONFERENCE THEME**

## **ELECTRONICS FOR HEALTHY LIVING**

#### The ISSCC 2011 Conference theme is:

#### "Electronics for Healthy Living"

Electronics play a significant role in enabling a healthier lifestyle. Technology in the hospital enables doctors to diagnose and treat illnesses that might have gone undetected just a few years ago. External monitors provide us with a good assessment of our health risk and vital-sign status. Those with chronic diseases can live a more normal life with internal and external electronic devices. In the future, Body Area Networks could be connected to a monitoring program running on our mobile phone. Those with disabilities also benefit from electronics that improve their lifestyle. Contributions to ISSCC are encouraged in support of this theme.

## **EVENTS**

#### TUTORIALS (SUNDAY, FEBRUARY 20, 2011)

• 9 90-minute Tutorials, each taught twice, by circuit experts from the International Technical Program Committee, serve to meet attendees` needs for introductory material in circuit specialties.

#### FORUMS (SUNDAY & THURSDAY, FEBRUARY 20 & 24, 2011)

• Circuit experts exchange information on their current research in an all-day informal environment.

**SPECIAL-TOPIC EVENING SESSIONS** (SUNDAY – TUESDAY, FEBRUARY 20-22, 2011)

- 6 Special-topic presentations, in which experts provide insight and background on a subject of current importance.

- Student Research Preview short student presentations of work-in-progress at Universities around the world.

#### EVENING PANELS (MONDAY – TUESDAY, FEBRUARY 21-22, 2011)

• 2 Panels in which industrial and academic experts debate a selected topic and field audience questions in a semi-formal atmosphere.

TECHNICAL SESSIONS (MONDAY – WEDNESDAY, FEBRUARY 21-23, 2011)

- 3 invited talks, and 1 distinguished panel presented in the Plenary Session.

- 211 technical papers presented in 28 Regular Sessions, highlighting the latest circuit developments.

#### **SOCIAL HOURS** (MONDAY – TUESDAY, FEBRUARY 21-22, 2011)

• Network with experts in a wide range of circuit specialties; meet colleagues in an informal exchange; browse the technicalbook exhibits!

#### SHORT COURSE (THURSDAY, FEBRUARY 24, 2011)

Intensive all-day course on a single topic, taught by world-class instructors, can serve to "jump start" a change in an engineer's circuit specialty.

## PAPER STATISTICS

### OVERALL:

- 3 papers invited

- 669 papers submitted to ISSCC 2011

- 211 papers accepted

- 80 papers from North America, including

- 36 Industry papers

- 43 University papers

- 1 Institution/Lab papers

- 69 papers from the Far East, including

- 30 Industry papers

- 38 University papers

- 1 Institution/Lab papers

- 62 papers from Europe, including

- 22 Industry papers

- 19 University papers

- 21 Institution/Lab papers

- 28 Sessions, over 3 days

| INTERNATIONAL SCOPE:                  | <u>2011</u> | <u>2010</u> | <u>2009</u> | <u>2008</u> |

|---------------------------------------|-------------|-------------|-------------|-------------|

| Americas:                             | 38 %        | 41 %        | 38 %        | 43 %        |

| Far East:                             | 33 %        | 31 %        | 35 %        | 28 %        |

| Europe:                               | 29 %        | 28 %        | 27 %        | 29%         |

| WIDE COVERAGE:                        | <u>2011</u> | <u>2010</u> | <u>2009</u> | <u>2008</u> |

| Analog:                               | 10 %        | 9 %         | 11 %        | 9 %         |

| Data Converters:                      | 8 %         | 7 %         | 7 %         | 10 %        |

| Energy-Efficient Digital:             | 6 %         | 6 %         | 6 %         | 5 %         |

| High-Performance Digital:             | 7 %         | 10 %        | 4 %         | 7 %         |

| Imagers, MEMs, Medical, and Displays: | 14 %        | 12 %        | 12 %        | 11 %        |

| Memory:                               | 10 %        | 11 %        | 9 %         | 12 %        |

| PLL:                                  |             | 6 %         |             |             |

| RF:                                   | 12 %        | 8 %         | 11 %        | 11%         |

| Technology Directions:                | 10 %        | 12 %        | 13 %        | 12%         |

| Wireless:                             | 11 %        | 11 %        | 13 %        | 11%         |

| Wireline:                             | 11 %        | 8 %         | 14 %        | 11%         |

© COPYRIGHT 2011 ISSCC-DO NOT REPRODUCE WITHOUT PERMISSION

## PLENARY SESSION

Paper 1.1: New Interfaces to the Body Through Implantable System Integration Steve Oesterle, Senior Vice President, Medtronic, Minneapolis, MN

This presentation will discuss:

- For the last 40 years, Moore's law has driven the semiconductor industry, enabling new interfaces to the world.

- This engine has provided enhanced sensing, processing, actuating, and communicating with the environment.

- A particular beneficiary has been, is, and will be healthcare.

- The first marked success was the implantable electronic pacemaker.

- Then cellular modulation schemes were developed to ameliorate neurological disorders.

- But, future developments must include a systems approach in the design of both implantable devices and the entire healthcare pathway.

- Implantable designs must heed three abstractions: device interface, information flow, and energy management.

- As Moore's law slows for simple planar scaling, packaging and other techniques introduce "More than Moore".

- In spite of obvious dramatic developments, much remains to be done: system-focused thinking is needed for individual device development, and for a more global approach to easing clinical burden with improved patient outcomes.

#### Paper 1.2:

## Game-Changing Innovation for Wireless Personal Healthcare and Lifestyle: Magical, Revolutionary and Low-Cost Product Opportunities

Jo De Boeck, Senior Vice President, imec, Leuven, Belgium

This presentation will discuss:

- Healthcare is increasingly reliant on silicon for disease-centric care, patient-centric decision making and therapy, proactive personalized ubiquitous diagnosis and treatment.

- Personalized predictive preventive participatory healthcare implies massive measurement, myriad data, and convenient ICT infrastructure.

- Future data will be gathered "on the move" in residential and desolate settings by minimally-trained individuals.

- Currently, self-reported data is key to clinical trials, diagnosis, treatment progress, and assessment of quality of life. But, it is not reliable!

- In the future, connected devices which provide such data in acceptable unobtrusive ways, with guaranteed quality, privacy, and identity, will make all the difference.

- Such monitoring can potentially capture high-yield micro-events that predict upcoming problematic situations.

- Currently, wireless ECG patches are starting to impact care efficiency; in the future, multi-sensory smart patches will be a game changer.

- Such patches will connect to healthcare infrastructure will likely smell, listen, and feel.

- But, change in interaction between the medical and electronics communities is necessary, as illustrated by current world-wide trials of wireless sensors and body-area networks.

- Body-area networks are likely to foster and strengthen the individual in their search for better quality of life.

#### Paper 1.3: Eco-Friendly Semiconductor Technologies for Healthy Living Oh-Hyun Kwon, President, Samsung Electronics, Giheung, Korea

This presentation will discuss:

- Pollution has negatively affected the positive contributions of technological development.

- All industries must commit themselves to rescuing us from this peril!

- A dominant source of pollution is energy consumption.

- Semiconductor manufacturers can contribute directly and indirectly in several ways: reduce energy required in their basic manufacturing processes; reduce energy required by all products; encourage low-energy replacement by electronics of high-energy mechanisms.

- Semiconductor efficiency can be achieved by improved design including architecture, design methodology, process technology, and packaging.

- Pollution reduction can be achieved also by improved interaction with other industries: software developers and end-users for overall product efficiency, power-equipment manufacturing, generation, and distribution companies.

- To reduce power consumption of the semiconductor manufacturing industry itself, a strong cooperation with fabrication-equipment manufacturers is necessary.

- Recent examples of all of these many approaches include power-efficient multi-core processors, green memory solutions, 3D packaging, low-voltage low-leakage process technologies, low-power design methodologies, and implementing technology for smart-grid power systems.

- For an eco-friendly future, the IC manufacturing industry has lots of work ahead!

#### 1.4 Technology Roundtable: Beyond the Horizon: The Next 10x Reduction in Power – Challenges and Solutions

In this inaugural Plenary Technology Roundtable, experts will discuss opportunities for achieving the next order-ofmagnitude reduction in energy consumption across various domains, including analog, digital, RF, and memory. The role of process-technology innovation and CAD tools will also be discussed.

Three domain experts will challenge the six distinguished panelists to suggest directions for the future, and help create a roadmap for next-generation energy-efficient electronics.

Moderator: Jan Rabaey, Professor, University of California, Berkeley, Berkeley, CA

Panelists: Jack Sun, CTO, TSMC, Hsin-Chu, Taiwan Dan Dobberpuhl, Consultant, Monterey, CA

Kiyoo Itoh, Fellow, Hitachi, Tokyo, Japan

Philippe Magarshack, Group Vice President, STMicroelectronics, Crolles, France Asad Abidi, Professor, University of California, Los Angeles, Los Angeles, CA

Hermann Eul, Executive Vice President, Infineon, Neubiberg, Germany

Domain Experts: **Hugo De Man**, Professor Emeritus, imec, Leuven, Belgium **Mark Horowitz**, Professor, Stanford University, Stanford, CA **Takayasu Sakurai**, Professor, University of Tokyo, Tokyo, Japan

## TECHNICAL HIGHLIGHTS

#### Analog:

- A digital PLL incorporates a new technique to remove the effects of power-supply noise that have plagued prior PLLs when integrated in system-on-chip ICs. Toshiba uses a digital calibration signal to facilitate cancellation of the deleterious effects of power-supply disturbances. **[5.6]**

- Highly efficient LED lamps can now be driven directly from the wall! A new BiCMOS chip designed by Fairchild Semiconductor connects to 110 and 220 VAC, and delivers a power factor of 0.98 and 0.92 respectively into a 5W LED.

[13.1]

- Extraordinary DC performance is now combined with very low noise in a chopper operational amplifier. Analog Devices has established a new world record of 5.9nV/√Hz achieved with a maximum of only 0.78µV of input offset. **[13.4]**

- Advanced microprocessors can now contain their own power regulators: an extremely efficient DC-DC converter has been implemented by Arizona State University and JPL in an advanced CMOS digital technology; this technology is optimized for digital application, and previously thought incapable of supporting such analog functionality; the design exploits its dense and power-efficient digital capabilities to implement digital control algorithms. [22.2]

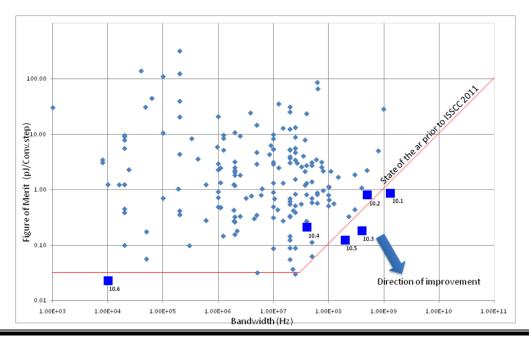

#### Data Converters:

- Unprecedented level of performance in an ADC! NXP describes a hierarchical interleaving of large numbers of Successive-Approximation- Register (SAR) ADCs which enable 10-bit operation at 2.6GS/s, while achieving more than 7 ENOB with less than 0.5W power dissipation. [10.1]

- Unprecedented combination of ENOB, bandwidth and power-efficiency in an ADC. Broadcom presents a 12b 800MS/s Nyquist-rate ADC with less than 105mW of power dissipation, by combining a dual-residue topology with simple and fast background offset calibration. [10.3]

- Highest DAC sampling rate ever reported! Ciena presents a 56GS/s 6-bit DAC in 65nm standard CMOS. [10.8]

- Never before reported bandwidth! NXP and Delft University of Technology present a 125MHz continuous-time deltasigma modulator in 45nm CMOS which achieves a dynamic range of 70dB. [27.1]

- Record low supply voltage operation of a Delta-Sigma modulator! The K.U. Leuven design achieves 61dB of SNDR, using only 7.5uW of power from a 250mV supply while operating at a bandwidth of 10kHz. [27.4]

#### **Energy-Efficient Digital:**

- A never before seen level of 3D multimedia experience is demonstrated. A chip from National Taiwan University shows a record high resolution of 4096 x 2160 pixels with free view point at a previously unseen frame rate of 216 frames per second. [7.1]

- The first 28 nm digital signal processor is presented by Texas Instruments and MIT. Low-voltage operation at 0.6 V is demonstrated. [7.5]

- The lowest energy-per-operation for a wireless sensor-node processer is demonstrated by the imec and NXP. The energy efficiency is as low as 10 pJ per clock cycle. [19.1]

- Pioneering work is presented for ultra-low-voltage standard cells. The corresponding chip from the University of Freiburg and HSG-IMIT, shows digital-logic gates operating with a supply voltage as low as 62mV. **[19.5]**

#### High-Performance Digital:

- Highest frequency in microprocessor history! The IBM zEnterprise 196 server chip runs at 5.2GHz in 45nm CMOS with four processing cores and 30MB of cache memory using 1.4 billion transistors. [4.1]

- Highest x86 server processor core count! The Intel Bangalore Westmere-EX packs 10 dual-threaded cores on a single die, together with the L3 cache and ring interconnect in a 32nm CMOS process. [4.3]

- Highest energy efficiency in a processor! The Godson-3B processor from the Chinese Academy of Sciences is an 8-core design implemented on 65nm CMOS. Its peak performance is 128GFlops for double-precision with 40W power, thereby delivering an astonishing energy efficiency of 3.2GFlops/Watt. [4.4]

- Highest transistor count and most complex microprocessor ever developed! The Intel 32nm "Poulson" processor contains 3.1 billion transistors integrated onto a single 544mm<sup>2</sup> silicon die size. Eight processor cores and a total of 54MB of onchip cache are linked by an on-chip ring-like interconnect bus. [4.8].

- Two contenders for highest level of integration including graphics processing units (GPUs) on a single silicon die with multiple CPU cores. The 32nm Intel "Sandy Bridge" processor integrates four high performance x86 cores, an optimized GPU, dual-channel DDR3 memory controller, and a 20-lane PCIe interface [15.1]. The 40nm AMD "Zacate" processor integrates two x86 "Bobcat" cores (each with a 512KB L2 cache) with a dedicated Radeon HD5000 series graphics and multimedia engine, DDR3 memory controller, client northbridge, and a 4X PCIe link [15.4].

#### Imagers, MEMS, Medical and Displays (IMMD):

- New concepts in energy harvesting for autonomous systems! Several academic and industrial organizations report devices that utilize energy harvesting from photovoltaic, and mechanical (piezoelectric) processes, with one design even integrating the energy harvesting circuitry into the pixel structure itself. **[6.7, 6.8, 6.9]**

- First fully-implantable laser-based fluorescence detector. Stanford University's solution fits within a 1 cm<sup>3</sup> form factor weighing just 0.7g while achieving a 5x improvement in dynamic range, and a 10dB reduction in noise over conventional sample-and-hold-based solutions. **[17.5]**

- First bidirectional microdisplay enables eye-tracking on a head-mounted display. The Fraunhofer Institute for Photonic Microsystems integrates a 320x240 monochrome AMOLED display with a 160x120 image sensor in 0.35µm CMOS.

[17.8]

- Fastest frame rate ever reported for an image sensor! An academic and industrial consortium around DALSA deliver an

image sensor with a capture speed of 16Mframes/s. High light sensitivity is essential given the extremely high capture rate

so the sensor incorporates state-of-the-art design techniques to optimize light sensitivity, including Backside Illumination

(BSI) and Charge-Carrier Multiplication (CCM) for low-noise readout. [23.4]

- World's largest and most light-sensitive monolithic image sensor! Canon's new image sensor contains 1.6Mpixels with a 160µm pitch, and occupies an entire 12" (300mm) CMOS wafer. The huge pixel size, combined with a built-in 0 to 24dB programmable gain, enable an ultra-high light sensitivity of 25Melectrons/lux/sec. [23.5]

#### Memory:

- The smallest die size reported for a 64Gb MLC 2bit/cell NAND device at 151mm<sup>2</sup>. Toshiba and Sandisk provide new programming algorithms which improve the Data-Write throughput of the device by 5%. [11.1]

- First 32nm HKMG SOI SRAM employing bitline regulation and write-assist techniques. This IBM device enables low voltage operation down to 0.7V. [14.1]

- Smallest 28nm SRAM with a 0.12µm<sup>2</sup> bitcell. This design from MIT and TI enables high density embedded SRAM down to 0.6V for System-on-Chip Applications. [14.4]

- Highest data rate of 12.8GB/s in mobile wide-I/O DRAM. Using 512 bit I/O, 2-stacked 2Gb mobile I/O with micro-bumps and TSV technology, Samsung achieves 90% I/O-power reduction. [28.5]

- Highest density of 2Gb GDDR5 Graphics DRAM achieved using 40nm CMOS. Samsung achieves data rates of 7Gb/s/pin using a channel-crosstalk-equalization scheme. [28.6]

#### Radio Frequency (RF):

- New AD-PLL techniques remove impunity to interference in radio front ends enabling highly programmable radio front ends used in high-density environments. [3.1, 3.2]

- Radio receiver architecture has come full circle! Broadcom and UCLA will demonstrate the re-emergence of the oldschool super-heterodyne receiver in 65nm with fully-integrated high-Q IF filters, and UCLA will demonstrate that the similarly-aged super-regenerative receiver can be put to good use in a very compact 186GHz low-power imaging application also in 65nm CMOS. [3.5, 16.10]

- Revolutionary advancements in fundamental millimeter-wave technology blocks. A variety of industrial and academic researchers deliver innovative techniques that yield revolutionary millimeter-wave building blocks capable of operating at frequencies up to 300GHz. [16.2, 16.3, 16.5, 16.6, 16.7]

- New AD-PLL techniques dramatically enhance range and velocity resolutions of FMCW radars. An FMCW synthesizer radar by Toshiba achieves range and velocity resolutions of 10cm and 1.4km/h respectively thanks to a 2x wider bandwidth and 6x longer modulation period than previously reported solutions. **[16.8]**

- First demonstrations of linear PAs in CMOS. Intel and Samsung will deliver CMOS-only linear PA solutions addressing the WLAN and EDGE/GSM markets respectively. [24.2, 24.4]

- Demonstration of switched-capacitor techniques being applied to high-power signal processing. The University of Washington will demonstrate a 2GHz power amplifier delivering 25dBm, using purely switched-capacitor techniques for signal modulation. [24.3]

- Record-low power levels for a 60GHz PA in 65nm CMOS. UC Berkeley will demonstrate 18.6dBm saturation power using only 0.28mm<sup>2</sup> of silicon area! [24.5]

#### Technology Directions (TD):

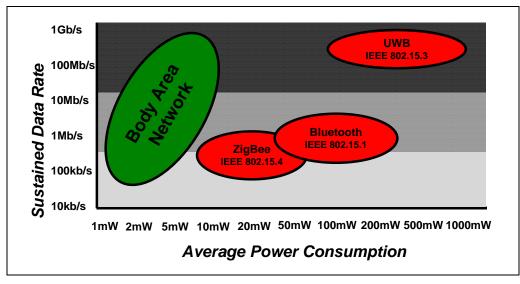

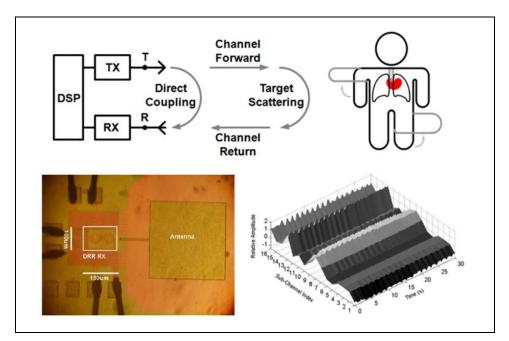

- A transceiver with ultra low energy (0.24nJ/b) and high sensitivity (250µV) for body-communication-channel-based Body Area Network. A design by KAIST has the potential to revolutionize wearable and continuous healthcare monitoring. [2.1]

- A 15-patch ultra-lightweight (400mg) low-power wearable sensor network. A design by KAIST, consuming less than 450µW, makes sleep-apnea monitoring and detection a true therapeutic solution! **[2.2]**

- Technology and architectural choices enable critical building blocks for Terahertz (300GHz to 3THz) based imaging. CEA-LETI-MINATEC and Universite Montpellier use a pixel embodying a single CMOS transmitter integrated with a bowtie antenna and low-noise amplifier; University of Wuppertal and IHP will present an 820GHz SiGe based chipset for THz active imaging. [2.5, 12.5]

- A low start-up voltage scavenging converter and a stand-alone self-powered electrical outlet energy monitor will accelerate the remote-sensor market. The University of Tokyo and STARC will present a voltage converter requiring only 95mV for start-up, with 72% system efficiency; NEC will present a realtime non-contact power-line-current sensor for home energy management. [12.1, 12.3]

- The world's first flexible organic substrate microprocessor! imec, et. al. will present an 8-bit processor running 6 instructions per second which foreshadows the future "Internet of things". [18.1]

#### Wireless:

- First fully-integrated CMOS 60GHz transceivers reported, that address the new Wireless-HD and WiGig standards. Researchers from CEA-LETI-MINATEC and STMicroelectronics will deliver an industrially-packaged Wireless-HD solution capable of 3.8Gb/s operation, using an HTCC substrate, including glass antennas. SiBeam describes a 65nm chipset that supports the maximum Wireless-HD and WiGig data rates, using 32 transmitter and 32 reciever antennas. [9.2, 9.3]

- First 3-stream 3x3 MIMO WLAN SoC to improve throughput, range, and link robustness. A chip designed by National Taiwan University integrates three dual band WLAN transceivers and is backward-compatible with legacy IEEE 802.11 a/b/g networks. [9.6]

- First-reported single transceiver showing diversity-performance gains of 50-120%. A consortium including ST-Ericsson, Ericsson, and Lund University will deliver the smallest reported WCDMA/EDGE diversity receiver with a DigiRF interface. [21.2]

- Highest level of integration reported for a cellular chipset. Qualcomm will deliver a fully-integrated solution containing an embedded EDGE/UMTS RF section, digital baseband processor, memories, and audio processor, all on a single SoC. In addition, a novel DPLL architecture ensures very-low peak transmitter-battery current for GSM low-band operation. [21.3]

- First-reported all-digital multi-mode transmitter meeting the stringent 3GPP RX-band noise requirements. A collaboration between Infineon Technologies and DICE will deliver a low-power polar architecture with lowest-reported power consumption. [21.7]

- New RFID sensor with the widest frequency range ever reported. Collaboration between Graz University and Infineon yields an ultra-low-power sensor node, employing innovative design techniques to support a frequency range of 13MHz to 2.45GHz, while minimizing power dissipation by an additional 70% over the current state-of-the-art. [26.1]

- First self-correlation-based RFID reader is demonstrated. Researches from KAIST and PHYCHIPS will demonstrate an RFID reader which isolates small back-scattered sensor signals from self-leakage in the transmitter, eliminating the need for large off-chip isolators. [26.2]

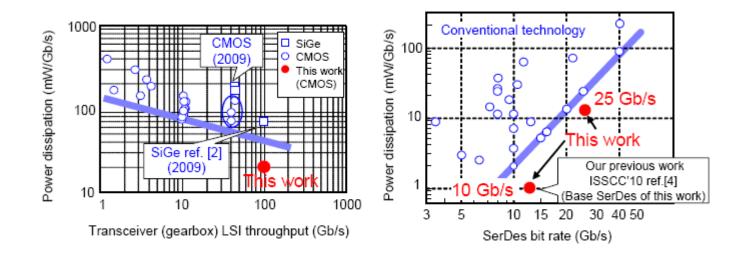

#### Wireline:

- The best equalization capability ever demonstrated by a receiver! Researchers from Fujitsu Laboratories will describe the first reported receiver that is able to accurately reconstruct an incoming signal while receiving less than 1% of the transmitted data energy! [20.1]

- New low-cost plastic materials are being developed to carry data signals. A co-operative venture between Sony and Caltech combines a new technology, plastic channel waveguides, and full-duplex transceiver technology to create a low-cost 25Gb/s interconnect. [8.5]

- The world's first CMOS 100Gb/s Ethernet gearbox has been developed! Engineers from Hitachi will present a 10:4 CMOS MUX/DEMUX gearbox for 100Gb/s Ethernet operation. **[8.4]**

- A new record for the "greenest" interface for display panels has been set! Researchers from Seoul National University will present a new video interface in 130nm CMOS that has both lower power and smaller area than the existing state-of-the-art. [25.8]

- The most sophisticated CMOS transceivers ever demonstrated. Engineers from LSI and Texas Instruments, along with Arda Technologies, have independently developed the first generation of transceivers with 10 or more taps of DFE correction and an operating rate of over 14Gb/s. **[20.2, 20.3]**

## EDUCATIONAL EVENTS

#### TUTORIALS

- T1: Integrated LC Oscillators Pietro Andreani (Lund University)

- T2: Embedded Memories for SoC Harold Pilo (IBM)

- T3: Ultra-Low Power and Low Voltage in Digital Design Jos Huisken (imec)

- T4: Layout The Other Half of Nanometer Analog Design Jed Hurwitz (Gigle Networks)

- T5: DPLL-Based Clock and Data Recovery John T. Stonick (Synopsys)

- T6: Practical Power-Delay Design Trade-Offs Tim Fischer (AMD)

- 77: Distortion in Cellular Receivers Sven Mattisson (Ericsson)

- **T8:** Noise Analysis in Switched-Capacitor Circuits Boris Murmann (Stanford University)

- **T9:** Interfacing Silicon with the Human Body Tim Denison (Medtronic)

#### SHORT COURSE

SC1: Cellular and Wireless LAN Transceivers: From Systems to Circuit Design Hooman Darabi (Broadcom), Frank Op't Eynde (Audax Technologies), Behzad Razavi (University of California Los Angeles), Bogdan Staszewski (TU Delft)

#### FORUMS

#### F1: Advanced Transmitters for Wireless Infrastructure

Earl McCune (RF Communications Consulting), Renato Negra (RWTH Aachen University), Klaas Bult (Broadcom Netherlands BV), Ian Galton (University of California San Diego), Olivier Charlon (Scintera Networks Inc.), Martin Clara (Lantiq A GmbH), Bumman Kim (Pohang University of Science and Technology)

#### F2: Ultra-Low Voltage VLSIs for Energy-Efficient Systems

Ticky Thakkar (Intel), Philip K.T. Mok (Hong Kong University of Science and Technology), Frederic Boeuf (ST Microelectronics), Takayasu Sakurai (University of Tokyo), Kaushik Roy (Purdue University), Guido De Sandre (ST Microelectronics), Baher Haroun (Texas Instruments), Peter Kinget (Columbia University), Akira Matsuzawa (Tokyo Institute of Technology)

#### F3: Towards Personalized Medicine and Monitoring for Healthy Living

Carlotta Guiducci (EPFL), Ken Shepard (Columbia University), Yogesh Gianchandani (University of Michigan), Jerald Yoo (Masdar Institute of Science and Technology), Shey-shi Lu (National Taiwan University) Wentai Liu (University of California Santa Cruz), Stefan Launer (Phonak/Sonova), Rahul Sarpeshkar (MIT), Chris Toumazou (Imperial College)

#### F4: Design of "Green" High-Performance Processor Circuits

Matthias Knoth (MIPS), William Dally (NVIDIA), Anthony Hill (Texas Instruments), David Flynn (ARM), Masafumi Takahashi (Toshiba Corporation), Ronald Preston (Intel Corporation), David Blaauw (University of Michigan), Sung Bae Park (Samsung Electronics)

#### F5: Image Sensors for 3D Capture

Ian Underwood (University of Edinburgh), Peter Seitz (CSEM), Pierre Magnan (ISAE), Cyrus Bamji (Canesta), Bernhard Buettgen (MESA Imaging), Edoardo Charbon (TU Delft), Shingo Mandai (University of Tokyo), Ralph Etienne-Cummings (Johns Hopkins University), Keith Fife (Ubixum)

#### F6: High-Speed Transceivers: Standards, Challenges, and Future

Jared Zerbe (Rambus), Thomas Toifl (IBM Research GmbH), Marcus van Ierssel (Snowbush IP), Takeshi Horie (Fujitsu Laboratories), Daniel Weinlader (Synopsys), Fulvio Spagna (Intel), Anthony Fraser Sanders (Lantiq Deutschland)

## **EVENING SESSIONS**

#### SPECIAL TOPICS

#### ES0: Student Research Preview

Organizers: Jan Van der Spiegel (University of Pennsylvania), SeongHwan Cho (KAIST)

ES1: Data-Converter Breakthroughs in Retrospect Hae-Seung Lee (MIT), Stephen Lewis (UC Davis), Doug Mercer (Analog Devices), Bruce Wooley (Stanford University)

#### ES2: Wireless Sensor Systems: Solutions & Technology Masayoshi Esashi (Tohoku University), Kris Pister (Dust Networks), Raphaël Salot (CEA-LITEN), Dennis Sylvester (University Of Michigan), Ruud Vullers (IMEC)

## ES3: Future System and Memory Architectures: Transformations by Technology and Applications

Jim Kahle (IBM), Stephen Pawlowski (Intel), Tomofumi Shimada (Toshiba), Raj Talluri (Qualcomm)

#### ES4: Body Area Networks (BAN): Technology, Solutions, and Standardization Arthur Astrin (Astrin Radio), David Davenport (GE Global Research), Okundu Omeni (Toumaz UK), Huang-Bang Li (NICT), Anuj Batra (Texas Instruments), Seong-Jun Song (Samsung)

#### ES5: Gb/s+ Portable Wireless Communications Jeff Gilbert (SiBEAM), Jri Lee (National Taiwan University), Ali S. Sadri (Intel), Rolf De Vegt (Qualcomm)

#### ES6: Technologies for Smart Grid and Smart Meter Keith Findlater (Gigle Networks), Sang-Gug Lee (KAIST), Martin Manniche (GreenWave Reality), Mick Mueck (Analog Devices)

### PANELS

#### EP1: Good, Bad, Ugly - 20 Years of Broadband Evolution: What's Next? David Borison (Ralink), Larry DeVito (Analog Devices), Sven Mattisson (Ericsson),

Stephen Palm (Broadcom), Michiel Steyaert (KU Leuven), Eric Yeh (MediaTek)

#### EP2: 20/22nm Technology Options and Design Implications

Mark Bohr (Intel), Min Cao (TSMC), Koichiro Ishibashi (Renesas), Bill Liu (GlobalFoundries), Ghavam Shahidi (IBM)

## SUBCOMMITTEE CONTRIBUTIONS

| SUBCOMMITTEE                             | SESSIONS   | EVENING<br>SESSIONS | EVENING<br>PANELS | TUTORIALS | FORUMS | SHORT<br>COURSES | PRESS COPY<br>PAGE #'S                    |

|------------------------------------------|------------|---------------------|-------------------|-----------|--------|------------------|-------------------------------------------|

| ANALOG                                   | 5, 13, 22  | ES6                 |                   | T1        | F3, F6 |                  | 141, 153, 164                             |

| DATA<br>CONVERTERS                       | 10, 27     | ES1                 |                   | T2        | F1     |                  | 147, 168                                  |

| ENERGY-<br>EFFICIENT<br>DIGITAL          | 7,19       | ES2                 |                   | Т5        | F4     |                  | 143, 144, 161                             |

| HIGH-<br>PERFORMANCE<br>DIGITAL          | 4, 15      | ES3                 | EP2               | ТЗ        | F4     |                  | 137, 138, 139, 140,<br>155                |

| IMAGERS,<br>MEMS, MEDICAL<br>AND DISPLAY | 6, 17, 23  | ES4                 |                   | T4        | F3, F5 |                  | 142, 159                                  |

| MEMORY                                   | 11, 14, 28 | ES2, ES3            |                   | Т6        | F2     |                  | 148, 154, 169                             |

| RF                                       | 3, 16, 24  |                     | EP1               | T7        | F1, F3 | SC1              | 157, 165                                  |

| TECHNOLOGY<br>DIRECTIONS                 | 2, 12, 18  | ES4                 |                   |           | F3     |                  | 134, 135, 136, 149,<br>150, 151, 152, 160 |

| WIRELESS                                 | 9, 21, 26  | ES5                 |                   | Т8        | F1, F3 |                  | 146, 163, 167                             |

| WIRELINE                                 | 8, 20, 25  |                     | EP1               | Т9        | F2, F6 |                  | 145,162,166                               |

## ANALOG Subcommittee

© COPYRIGHT 2011 ISSCC-DO NOT REPRODUCE WITHOUT PERMISSION

## **ISSCC 2011 – ANALOG**

Subcommittee Chair: Bill Redman-White, NXP/Southhampton University, UK Press Designate: Ian Galton, University of California San Diego, San Diego, CA

## OVERVIEW

#### CONTEXT AND PRESENT STATE OF THE ART

- Despite the trend toward digital, analog circuits are not only still required in modern communication and computing systems, but their required performance is higher than ever.

- Digital circuits such as microprocessors drive the market, so the evolution of integrated circuit (IC) technology (as described by Moore's Law), has sacrificed traditional analog circuit performance in favor of digital circuitry.

- At each new IC technology node, analog-circuit designers are faced with increasingly challenging specifications, and traditional circuit-design techniques are increasingly ineffective. One of the few options open to analog-circuit designers to solve this problem is to incorporate digital signal processing techniques to overcome analog-circuit limitations.

#### **MOST-SIGNIFICANT PAPERS**

- A digital PLL incorporates a new technique to avoid an error source that has plagued prior digital PLLs. Politecnico di Milano use a 10-bit controllable delay element to cancel delta-sigma quantization noise. This, in turn, makes it possible to use a bang-bang phase detector in place of a noisy time-to-digital converter. [5.1]

- A digital PLL incorporates a new technique to remove the effects of power-supply noise that have plagued prior PLLs when integrated in system-on-chip ICs. Toshiba uses a digital calibration signal to facilitate cancellation of the deleterious effects of power-supply disturbances. [5.6]

- Highly efficient LED lamps can now be driven directly from the wall! A new BiCMOS chip designed by Fairchild Semiconductor connects to 110 and 220 VAC, and delivers a power factor of 0.98 and 0.92, respectively into a 5W LED.

[13.1]

- Extraordinary DC performance is now combined with very low noise in a chopper operational amplifier. Analog Devices has established a new world record of 5.9nV/√Hz achieved with a maximum of only 0.78µV of input offset. **[13.4]**

- Advanced microprocessors can now contain their own power regulators: an extremely efficient DC-DC converter has been implemented by Arizona State University and JPL in an advanced CMOS digital technology; this technology is optimized for digital application, and previously thought incapable of supporting such analog functionality; the design exploits its dense and power-efficient digital capabilities to implement digital control algorithms. [22.2]

### APPLICATIONS AND ECONOMIC IMPACT

- PLLs get quiet, even in a noisy environment, enabling higher-levels of integration and cost reduction. [5.1, 5.6]

- Sensing the impossible! High performance amplifiers designed for sensor applications make it possible to resolve smaller signals than ever thought possible, thereby enabling new sensor applications. **[13.4, 13.6, 13.8]**

- Power conversion goes digital advanced DSP techniques make complex embedded power-management systems feasible with low external-component count, even in nanometer technologies, enabling higher system integration and reduced system costs. [13.1, 22.2, 22.3, 22.4]

## SURVIVAL OF ANALOG TECHNIQUES!

With the increasing excitement over the digital world, people often forget that the real world is actually analog. Even though most of our technologies process information via computers and digital circuitry, the signals themselves originate and end up in analog form, such as sound and radio waves. Furthermore, all electronic circuits, whether analog or digital, must be supplied with power, and the power supply circuits are inherently analog. Nevertheless, digital circuits such as microprocessors, drive the market; so, integrated circuit (IC) technology (used in the factories that make integrated circuits) have been optimized relentlessly over the last 40 years to reduce the size, cost, and power consumption of digital circuits. This trend has made analog circuitry increasingly difficult to implement, yet the number of essential analog interface circuits and their performance requirements have increased.

Interestingly, analog designers have turned the curse of this trend away from "analog-friendly" IC technology into a cure. Rather than struggle to overcome the problem with traditional, time-tested analog circuit tricks, they have turned toward the utilization of digital signal-processing circuits, embedded within the analog-circuit blocks, to overcome analog-circuit limitations. This new approach blurs the distinction between analog and digital circuit design, but yields continued advances in the analog state-of-the-art. Increasingly, these techniques have enabled performance that matches, and now even exceeds, what was possible in traditional high-performance analog IC technology.

TRENDS

## DATA CONVERTERS Subcommittee

© COPYRIGHT 2011 ISSCC-DO NOT REPRODUCE WITHOUT PERMISSION

## **ISSCC 2011 – DATA CONVERTERS**

Subcommittee Chair: Venu Gopinathan, Texas Instruments, Bangalore, India Press Designate: Klaas Bult, Broadcom, Bunnik, The Netherlands

#### CONTEXT AND PRESENT STATE OF THE ART

- Digital Calibration to enhance data-converter performance is becoming common-place. [10.1, 10.2, 10.3, 10.5, 10.7, 27.2]

- Current state-of-the-art in CMOS DACs is 12GS/s. [10.8]

- The highest bandwidth in CMOS Delta-Sigma converters is several tens of MHz. [27.1]

#### **MOST-SIGNIFICANT PAPERS**

- Unprecedented level of performance in an ADC! NXP describes a hierarchical interleaving of large numbers of Successive-Approximation- Register (SAR) ADCs which enable 10-bit operation at 2.6GS/s, while achieving more than 7 ENOB with less than 0.5W power dissipation. [10.1]

- Unprecedented combination of ENOB, bandwidth and power-efficiency in an ADC. Broadcom presents a 12b 800MS/s Nyquist-rate ADC with less than 105mW of power dissipation, by combining a dual-residue topology with simple and fast background offset calibration. [10.3]

- Highest DAC sampling rate ever reported! Ciena presents a 56GS/s 6-bit DAC in 65nm standard CMOS. [10.8]

- Never before reported bandwidth! NXP and Delft University of Technology present a 125MHz continuous-time deltasigma modulator in 45nm CMOS which achieves a dynamic range of 70dB. [27.1]

- Now, digital correction technique improves the DAC performance of a high-speed Delta-Sigma ADC. This technique by Ulm University delivers 63dB SNDR at 10MHz bandwidth, and boosts the SFDR to an unprecedented 81dB. **[27.2]**

- Record low supply voltage operation of a Delta-Sigma modulator! The K.U. Leuven design achieves 61dB of SNDR, using only 7.5uW of power from a 250mV supply while operating at a bandwidth of 10kHz. [27.4]

#### APPLICATIONS AND ECONOMIC IMPACT

- A 2.6GS/s highly interleaved SAR ADC enables digitizing the entire TV-band which allows integration of multiple receivers on a single die, reducing system cost. [10.1]

- High-speed, low-power ADCs provide the technological building blocks which will enable 10G-ethernet applications for high-speed LAN, creating new and exciting opportunities for businesses and consumers alike. A side benefit of the

introduction of 10G solutions will be the continued commoditization of 1G solutions which will make existing high-speed LAN technologies even more economical. **[10.3]**

- A 56GS/s 65nm CMOS DAC allows integration with existing100Gb/s optical-link designs, reducing system cost. [10.8]

- Continued improvements in Delta-Sigma converter design propagates to the numerous applications in which they are used today such as GSM base stations and HD video systems. Ultimately this delivers higher quality solutions at better price points, resulting in improved feature sets and reduced costs for today's consumers. [27.1, 27.2]

- Driving Delta-Sigma data converter power consumption levels down into the µ-power range opens up exciting new application spaces where energy harvesting can be used to create truly autonomous systems such as portable or implantable medical sensors and diagnostic tools! [27.4]

## ENERGY-EFFICIENT DIGITAL Subcommittee

## **ISSCC 2011 – ENERGY-EFFICIENT DIGITAL**

Subcommittee Chair: Tzi-Dar Chiueh, National Taiwan University, Taipei, Taiwan Press Designate: Alice Wang, Texas Instruments, Dallas, TX

## OVERVIEW

#### CONTEXT AND PRESENT STATE OF THE ART

- Existing TV sets and set-top boxes have limited 3D capability and require shuttered glasses to look at interleaved frames [7.1, 7.3]

- Industry is still pursuing technology scaling to provide ultra-low-power devices. [7.5]

- Current mobile devices (such as, smart phones) have internet connectivity, but are still in need of more multimedia functionality with minimal power dissipation [7.6, 7.7, 7.8, 19.6]

- Deployment of wireless sensor networks is limited by the energy efficiency of the internal processors. The inability to operate at sub-threshold supply voltages prevents exploitation of the huge potential of wireless sensor networks in biomedical and other monitoring applications. [19.1, 19.2, 19.5]

#### **MOST-SIGNIFICANT PAPERS**

- A never before seen level of 3D multimedia experience is demonstrated. A chip from National Taiwan University shows a record high resolution of 4096x2160 pixels with free view point at a previously unseen frame rate of 216 frames per second. [7.1]

- The first 28nm digital signal processor is presented by Texas Instruments and MIT. Low-voltage operation at 0.6V is demonstrated. [7.5]

- The lowest energy-per-operation for a wireless sensor-node processer is demonstrated by the imec and NXP. The energy efficiency is as low as 10pJ per clock cycle. [19.1]

- Pioneering work is presented for ultra-low-voltage standard cells. The corresponding chip from the University of Freiburg and HSG-IMIT, shows digital-logic gates operating with a supply voltage as low as 62mV. **[19.5]**

- An unprecedented combination of increased energy efficiency and high performance for Fourier-transform block is demonstrated. The University of Michigan and Arizona State University will present a chip that consumes only 17.7nJ per transform with a record performance of 30MHz at a 0.27V supply voltage [19.6]

#### APPLICATIONS AND ECONOMIC IMPACT

- The electronic entertainment market is a financial juggernaut. An immersive unencumbered 3D experience will further boost this market to unprecedented heights and help make 3D television a standard in every household. [7.1, 7.3]

- Enhanced multimedia functions and high-data-rate connectivity make it possible to watch movies or television on every smart phone. This will further enhance the economic potential of the mobile market. **[7.2, 7.3, 7.4]**

- Ultra-high-efficiency electronic systems are essential to support applications that enhance human comfort and health. This is especially important for society's aging population. **[19.2, 19.5, 19.6]**

## HIGH-PERFORMANCE DIGITAL SUBCOMMITTEE

$\ensuremath{\textcircled{\sc c}}$  Copyright 2011 ISSCC—Do Not Reproduce Without Permission

## **ISSCC 2011 – HIGH-PERFORMANCE DIGITAL**

Subcommittee Chair: Stefan Rusu, Intel, Santa Clara, CA Press Designate: Sonia Leon, Intel, Santa Clara, CA

## OVERVIEW

#### CONTEXT AND PRESENT STATE OF THE ART

- This year's ISSCC processor lineup contains several record breaking processors enabled by engineering innovations in state-of-the-art 32nm manufacturing processes. Both general purpose and specialized SoC processors for graphics and multimedia are being integrated on a single silicon die to reduce system power and cost.

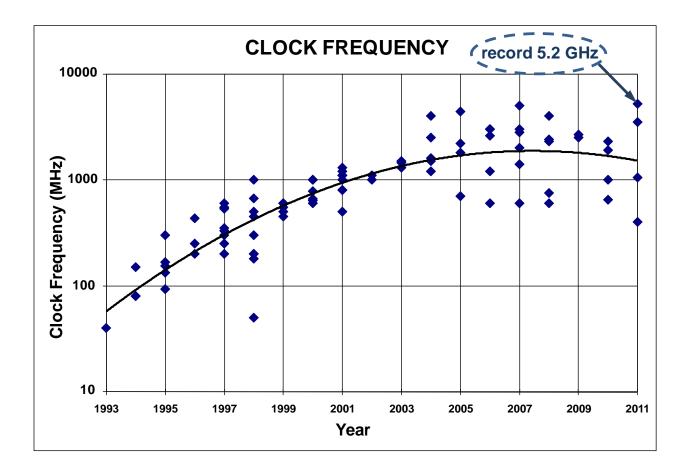

- Enterprise processors [Session 4] feature the fastest clock frequencies, the highest x86 core counts, the highest energy efficiencies, and the highest transistor counts ever achieved in commercial microprocessors.

- Integration rules! High performance SoC processors [Session 15] are integrating other chips and components from the system onto the processor die. This not only enables better use of the available silicon area, it also improves communication, reduces system complexity and cost, and lowers overall system power.

#### **MOST-SIGNIFICANT PAPERS**

- Highest frequency in microprocessor history! The IBM zEnterprise 196 server chip runs at 5.2GHz in 45nm CMOS with four processing cores and 30MB of cache memory using 1.4 billion transistors. **[4.1]**

- Highest x86 server processor core count! The Intel Bangalore Westmere-EX packs 10 dual-threaded cores on a single die, together with the L3 cache and ring interconnect in a 32nm CMOS process. **[4.3]**

- Highest energy efficiency in a processor! The Godson-3B processor from the Chinese Academy of Sciences is an 8-core design implemented on 65nm CMOS. Its peak performance is 128GFlops for double-precision with 40W power, thereby delivering an astonishing energy efficiency of 3.2GFlops/Watt. [4.4]

- Highest transistor count and most complex microprocessor ever developed! The Intel 32nm "Poulson" processor contains 3.1 billion transistors integrated onto a single 544mm<sup>2</sup> silicon die size. Eight processor cores and a total of 54MB of on-chip cache are linked by an on-chip ring-like interconnect bus. **[4.8]**.

- Two contenders for highest level of integration including graphics processing units (GPUs) on a single silicon die with multiple CPU cores. The 32nm Intel "Sandy Bridge" processor integrates four high performance x86 cores, an optimized GPU, dual-channel DDR3 memory controller, and a 20-lane PCIe interface [15.1]. The 40nm AMD "Zacate" processor integrates two x86 "Bobcat" cores (each with a 512KB L2 cache) with a dedicated Radeon HD5000 series graphics and multimedia engine, DDR3 memory controller, client northbridge, and a 4X PCIe link [15.4].

#### APPLICATIONS AND ECONOMIC IMPACT

- The drive to integrate dozens of cores and billions of transistors on a single die is required to feed today's insatiable demand for computation. The exploding core counts and heterogeneous integration enabled by billion plus transistor designs has required fast-paced architectural and circuit innovations in on-chip networks since integrated components need to transfer data at a pace that matches their computational ability. These innovations are enabling significant advances in energy-efficiency and application throughput on systems with a large number of cores. **[4.1, 4.3]**

- Innovative enterprise processors and design components achieve new heights of performance, integration, and energy

efficiency. By continuing to deliver exponentially increasing performance and capability, these efficient engines will enable

computers to analyze the world's most challenging scientific problems, and manage the corresponding increasing

demands of the ever-expanding global IT infrastructure. [Session 4]

- Processors are integrating other chips and components from the system onto the processor die. This trend not only

enables better use of the available silicon area, it also improves communication, reduces system complexity, and lowers

overall system power. More importantly, the higher levels of integration also enable lower overall system cost. This means

one overwhelming thing for the consumer: more bang for the buck! [Session 15]

### TRENDS IN PROCESSORS PRESENTED AT ISSCC

While process technology continues its onward advancement, enabling integration on massive scales, this year's processors come from wide technological backgrounds. New ground is broken in key areas of transistor integration, performance per unit power, and functional integration. This is accomplished across a wide range of process technologies – 65nm, 45nm, 40nm, and 32nm bulk and SOI CMOS technologies.

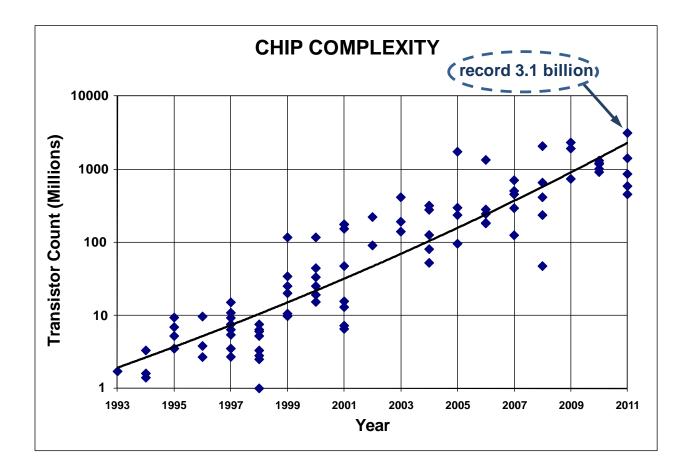

The chip-complexity chart below shows the trend in integrating transistors on a single chip over the past two decades. While the 1 billion limit was passed some 5 years ago, this year marks the first commercial product exceeding 3 billion transistors on a single die with the 32nm Intel Itanium Processor. The massive integration continues to drive the inclusion of large caches on-die as we see with 30MB on IBM's zEnterprise, and 54MB on the 32nm Intel Itanium.

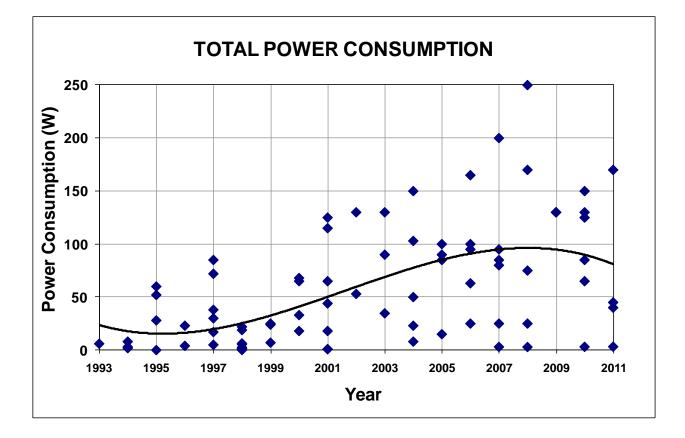

Aggressive processor power management and system-wide power optimization has become a requirement as technology has enabled the increasing trend of system integration onto the processor die. The trend of flat-to-down power in these systems continues as engineers leverage low-power design features to squeeze performance within existing power budgets. For example, the IBM zEnterprise system achieves a 20% frequency boost to a mind-numbing 5.2GHz with no power envelope increase over prior generation devices. The Godson-3B processor's focus on power enables that device to consume only 40W. The increased focus on power is helping rein in the immense demands, which PCs, servers, data centers, and similar systems put on power grids. The result will be lower cost, less cooling demands, and a greener product.

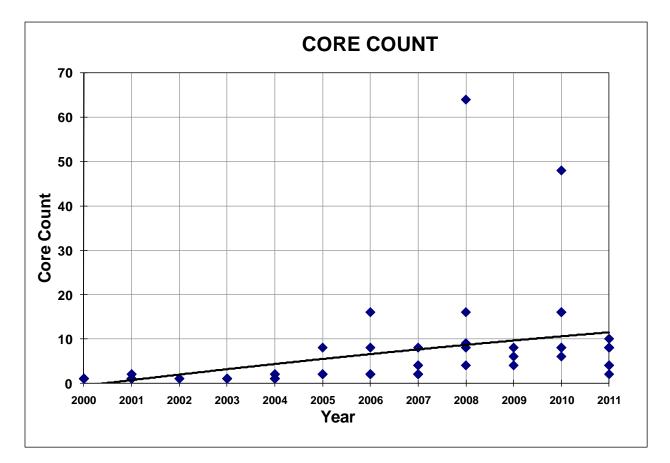

As a consequence of lower-power design requirements, system architects have been forced to innovate using multiple processor cores typically running parallel threads at lower frequencies. This enables processors to turn off when not actively doing computations. While ISSCC 2011 does not break ground in maximum core count, the body of work continues to emphasize this growing trend – IBM's zEnterprise is a 4-core machine, the Intel Westmere-EX delivers a 10-core solution, China's Godson-3B features 8 cores, and AMD's Bulldozer also delivers an 8-core CPU. This flexibility and scalability will enable adaptable system power profiles, further reducing power consumption and improving the end-user experience, as our multi-tasking lifestyle evolves.

These trends in integration, power consumption, and parallel computation, bring new challenges to processor development: New techniques are required to ensure robustness to power supply fluctuations; and improvements in power/clock delivery networks are required as multiple voltage domains become de facto on these chips. ISSCC 2011 will highlight many of these new building-block technologies.

© COPYRIGHT 2011 ISSCC—DO NOT REPRODUCE WITHOUT PERMISSION

TRENDS

## IMAGERS, MEMS, MEDICAL & DISPLAYS SUBCOMMITTEE

## **ISSCC 2011 – IMAGERS, MEMS, MEDICAL, AND DISPLAY**

Subcommittee Chair: Roland Thewes, TU Berlin, Germany Press Designate: Christoph Hagleitner, IBM Research, Switzerland

#### CONTEXT AND PRESENT STATE OF THE ART

- Micro-machined accelerometers and gyroscopes are commonly found in today's smart phones. [6.1]

- Optical molecular imaging is emerging as a powerful preclinical research tool for investigating and quantifying molecular events in living subjects. **[17.5]**

- Energy-harvesting research continues to draw great interest but remains an idea in need of more proof-of-concept implementations. [17.8]

- Current image sensors can capture millions of frames per second. [23.4]

- Large-area image sensors are required for applications which require high light-sensitivity (e.g., night-recording). [23.5]

#### **MOST-SIGNIFICANT PAPERS**

- New concepts in energy harvesting for autonomous systems! Several academic and industrial organizations report devices that utilize energy harvesting from photovoltaic, and mechanical (piezoelectric) processes, with one design even integrating the energy harvesting circuitry into the pixel structure itself. [6.7, 6.8, 6.9]

- First fully-implantable laser-based fluorescence detector. Stanford University's solution fits within a 1 cm<sup>3</sup> form factor weighing just 0.7g while achieving a 5x improvement in dynamic range, and a 10dB reduction in noise over conventional sample-and-hold-based solutions. **[17.5]**

- First bidirectional microdisplay enables eye-tracking on a head-mounted display. The Fraunhofer Institute for Photonic Microsystems integrates a 320x240 monochrome AMOLED display with a 160x120 image sensor in 0.35µm CMOS.

[17.8]

- Fastest frame rate ever reported for an image sensor! An academic and industrial consortium around DALSA deliver an

image sensor with a capture speed of 16Mframes/s. High light sensitivity is essential given the extremely high capture rate

so the sensor incorporates state-of-the-art design techniques to optimize light sensitivity, including Backside Illumination

(BSI) and Charge-Carrier Multiplication (CCM) for low-noise readout. [23.4]

- World's largest and most light-sensitive monolithic image sensor! Canon's new image sensor contains 1.6Mpixels with a 160µm pitch, and occupies an entire 12" (300mm) CMOS wafer. The huge pixel size, combined with a built-in 0 to 24dB programmable gain, enable an ultra-high light sensitivity of 25Melectrons/lux/sec. [23.5]

### APPLICATIONS AND ECONOMIC IMPACT

- Energy harvesting circuits achieve power and efficiency levels which enable truly autonomous sensor systems that will allow the development of myriad new applications. [6.7, 6.8, 6.9]

- Fully-implantable optical molecular imaging devices enable new applications including early disease detection, therapeutic monitoring, and biological understanding. **[17.5]**

- The first bidirectional microdisplay paves the way for new smart-phone applications, and smaller handset designs due to the high level of integration achieved using a single device. **[17.8]**

- Image sensors with capture rates in the millions of frame-per-second range will enable new scientific breakthroughs for high-speed-imaging applications. [23.4]

- Large-area image sensors create new capture possibilities such as video recording of stars in the night sky, nocturnal animal behavior, and other low-light-level conditions. [23.5]

## **TRENDS IN IMAGING**

- CMOS Imagers are coming to the compact Digital Still Camera (DSC) markets!

- High Dynamic Range (HDR) is (finally!) introduced in low-cost consumer imaging.

- The pixel race is alive and well as pixel sizes continue to shrink. Pixel resolution over 10M are commercially available employing enhanced small-size pixels.

- Backside illumination is becoming an indispensable technology for gaining the competitive edge in CMOS imagers, enabling increased market share.

- High-speed low-power low-noise column-parallel ADCs are becoming a key technology for high-definition video imagers.

- Rapid increases in integrated logic functionality are driving a dramatic increase in imager functions and features.

- 3D imagers are becoming a very hot R&D topic given the current push toward 3D entertainment.

- Increasing R&D investment is predicted in forthcoming years for automotive imaging, and for 3-D range-finding and time-of-flight (TOF) applications.

## TRENDS IN DISPLAYS

- Chip-on-Glass (CoG) interfaces are becoming a common choice for high-speed interfaces in notebook applications. In addition, touch and 3D functionality are making their way into notebook PC's and LCD monitors.

- Small-sized display-driver ICs are seeing increased levels of integration, with the following features becoming commonplace: user-adjustable image enhancements, touch-sensor readouts and handlings, 3D-driving control signals, and temperature-sensor integration to minimize power consumption.

- Backlight strategies are seeing an increased level of effort and interest.

- Lots of attention is given to making displays "greener" (that is, more power-efficient, as well as using more environmentally-friendly manufacturing processes).

## **TRENDS IN MEDICAL**

- Huge R&D activities in the field of bio-potential sensors capable of measuring neural activity.

- Neural techniques continue to propagate into more therapeutic applications. Clinical trials are ongoing for early diagnosis of depression.

- Chemical sensing is gaining ground in a neurological clinical setting. A pilot study has been completed on monitoring acute activity in the brain.

- Longer-term monitoring is facing similar challenges to glucose sensing in Diabetes. The need for chronic chemical sensors is critical. The ultimate goal is the development of solutions corresponding to an artificial pancreas.

- Cardiac therapies are focusing on ultra-miniaturization of existing devices. The goal is to eventually eliminate the leads, thereby simplifying cardiac surgery, which is currently a very invasive procedure. In addition, there is a push for instrumenting stents with miniaturized technology to add diagnostic capability to these widely-used devices.

## TRENDS IN SENSORS AND MEMS

- Silicon MEMS resonators and oscillators are replacing quartz-based solutions. The market uptake for MEMS is growing exponentially.

- Single-packaged multiple-axis accelerometers and gyroscopes have been announced by several companies, including STmicroelectronics, Bosch, and Invensense. These devices are now widely used in game controllers and smartphones.

- 3-axis accelerometers and 3-axis magnetic field sensors are now becoming available.

# MEMORY Subcommittee

$\textcircled{C} \mathsf{COPYRIGHT} \ \texttt{2011} \ \texttt{ISSCC}{--}\mathsf{Do} \ \mathsf{NOT} \ \mathsf{Reproduce} \ \mathsf{Without} \ \mathsf{Permission}$

## **ISSCC 2011 – MEMORY**

Subcommittee Chair: Kevin Zhang, Intel, Hillsboro, OR Press Designate: Cormac O'Connell, TSMC, Ottawa, Canada

## OVERVIEW

#### CONTEXT AND PRESENT STATE OF THE ART

- The economics of Solid-State Discs (SSD) are driven by the price per bit of NAND-Flash versus that on a magnetic disc. Die size and process complexity directly contribute to SSD costs. Therefore smaller die contribute to lower price per bit, making SSD denser and cheaper. [11.1, 11.3, 11.8]

- Traditional non-volatile memories are facing ever increasing scaling challenges. New emerging memory technologies are being pursued to provide viable alternatives for future high-density and low-power applications. [11.2, 11.6, 11.7]

- SRAM continues to be the memory workhorse for embedded applications. SRAM bitcell scaling is experiencing increasing difficulty achieving those densities predicted by Moore's law. More advanced silicon technologies such as Hi-K/Metal-Gate (HKMG), along with advanced circuit techniques are required for 32nm and beyond. [14.1, 14.4]

- Graphics applications continue to drive the need for high-memory-bandwidths. With each generation, it becomes ever more important to achieve high-data-rate memory interfaces. [28.6]

- In mobile applications, low-power memory is essential to meet increasing performance while maintaining low power consumption. Through-Silicon Via (TSV) technology is emerging to provide optimum power/bandwidth solutions. **[28.5]**

#### **MOST-SIGNIFICANT PAPERS**

- The smallest die size reported for a 64Gb MLC 2bit/cell NAND device at 151mm<sup>2</sup>. Toshiba and Sandisk provide new programming algorithms which improve the Data-Write throughput of the device by 5%. [11.1]

- A very-high-speed 4Mb embedded SLC Resistive RAM with a 7.2ns Read-Write Random Access time and 160ns of MLC capability. High performance is achieved using a parallel-series reference cell scheme and a process and temperature aware dynamic bitline bias circuit. [11.2]

- First 32nm HKMG SOI SRAM employing bitline regulation and write-assist techniques. This IBM device enables low voltage operation down to 0.7V. [14.1]

- Smallest 28nm SRAM with a 0.12µm<sup>2</sup> bitcell. This design from MIT and TI enables high density embedded SRAM down to 0.6V for System-on-Chip Applications. [14.4]

- Highest data rate of 12.8GB/s in mobile wide-I/O DRAM. Samsung achieves 90% I/O-power reduction using 512 bit I/O, 2-stacked 2Gb mobile I/O with micro-bumps, and TSV technology. **[28.5]**

- Highest density of 2Gb GDDR5 Graphics DRAM achieved using 40nm CMOS. Samsung achieves data rates of 7Gb/s/pin using a channel-crosstalk-equalization scheme. [28.6]

#### APPLICATIONS AND ECONOMIC IMPACT

- The small die size for the 64Gb MLC NAND device will enable denser, lower-power solid-state discs (SSD) which are impacting almost every mobile consumer product from smartphones to digital camcorders. [11.1]

- Emerging non-volatile memory technologies include PCRAM, RRAM, and CBRAM. Any one of these technologies has the potential to change the industry and eventually supersede Flash, and even DRAM, as a mainstream memory technology [11.2, 11.6, 11.7]

- Improved SRAM designs offer lower power and improved robustness at low supply voltages, enabling dependable operation in the migration to deep submicron 32nm and 28nm CMOS. **[14.1, 14.3, 14.4]**

- The 2Gb GDDR5 Graphics DRAM will enable more lively gaming action for game consoles and graphic cards. [28.3]

- The mobile wide-I/O DRAM, which shows 4x higher data bandwidth than existing LPDDR2 DRAM, will increase the performance of mobile phones and smartphones. [28.5]

## **TRENDS IN MEMORY**

**Overall:** Memory design has seen a number of trends over the years: process technology has steadily reduced its minimum feature size; a wide variety of technology have been developed to improve packing-density; and a myriad of technology/circuit/system optimizations have been created to improve performance and reduce power dissipation. In addition, emerging technologies such as 3D chip stacking and new physical memory mechanisms are pushing the memory R&D frontier even-further forward. Some current state-of-the-art results from ISSCC 2011 include:

- 28nm 64Gb TLC NAND flash memory

- 7Gb/s-GDDR5 DRAM with 2Gb capacity

- 64Mb SRAM in High-κ Metal-Gate 32nm SOI technology with robust operation

- 28nm SRAM using 6T cells with low-voltage 0.6V operation

- Emerging memory technologies realizing non-volatile RAM: FeRAM (Ferrolectric RAM) with a novel sensing scheme, a fast read/write RRAM (Resistive RAM), and a large bandwidth CBRAM (Conductive-Bridging RAM) at 2.3GB/s.

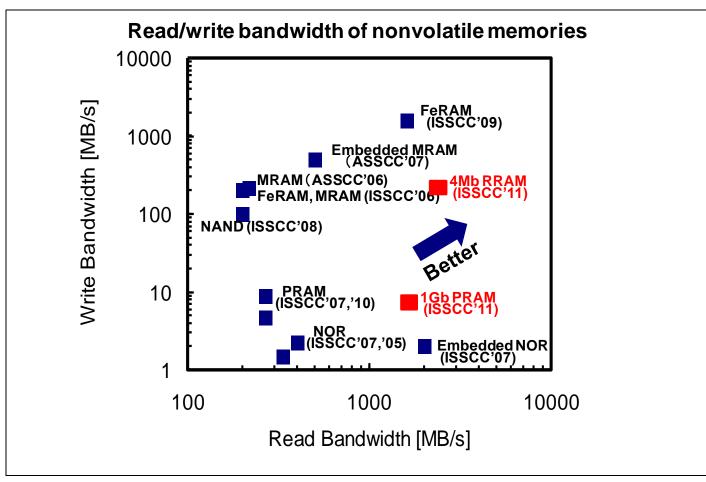

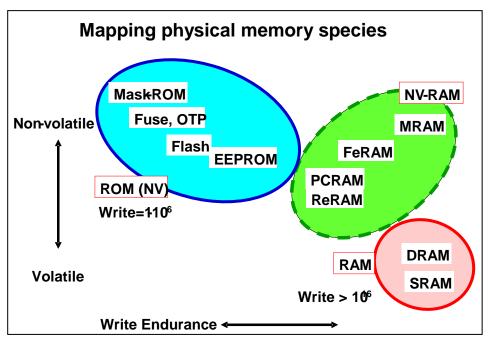

**Non-Volatile Memory (NVM):** The performance of persistent Non-Volatile RAM (NVRAM) has evolved over time, with ISSCC faithfully tracking these developments over the years. ISSCC 2011 will report the highest read/write bandwidths for emerging NVRAM technologies such as Phase Change Memory (PCRAM) and Resistive RAM (RRAM) resulting from the use of new circuit and device technology (**Figure 1**). This is presenting new opportunities for extending the memory technology spectrum, together with existing NAND/MRAM/FeRAM/PCRAM technologies, as shown in **Figure 2**. Commercial uses of these new breeds of NVRAM have been very slow to appear because of the rapid reduction of per-bit costs of conventional flash memory technologies already in the market. However, these new technologies are sure to capture some specific markets for lower-power or zero stand-by system implementation in the coming age of green technology.

**High-Performance Embedded Memory:** Embedded memory plays a crucial role in today's VLSI applications from high-performance computing to low-power consumer electronics. While scaling of technology feature size down to 32nm or 28nm has enabled everlarger and higher-performance on-die memories. However, scaling has also created growing challenges for the embedded memory designer. Growing device variability and power limitations are driving innovative solutions to maintain robustness and area-efficiency in such aggressively scaled memories. In particular, peripheral-circuit-assist features have become the key to maintaining cell read and write margins to enable low-voltage operation for dense SRAM caches. New strategies ranging from circuit-level techniques to fundamental changes in array architecture can also enable significant gains in area and power efficiency.

Figure 1: NVRAM Read/Write Bandwidth Trends

Figure 2: Comparison of NVRAM Technologies

#### TRENDS

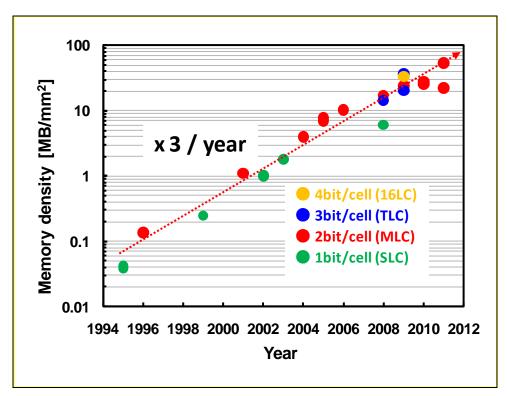

**NAND Flash Memory:** Significant developments in NAND flash memory over the past few years are resulting in high-density, low-power, and low-cost storage solutions that are enabling the replacement of traditional hard-disk storage with solid-state disks (SSDs). At ISSCC 2011, a 64Gb/die capacity will be demonstrated using 24nm technology with 2b/cell operation. With physical scaling down accompanied by advancing multi-level-storage-cell concepts, a 64Gb/die capacity has been demonstrated in 24nm technology with 2 bits/cell operation. **Figure 3** shows the observed trend in NAND flash capacities presented at ISSCC over the past 17 years. Unfortunately, as process feature size shrinks, error rates continue to rise, requiring system designers to develop more-sophisticated controllers to offset this issue, some of which are utilized outside the NAND silicon in the system memory controller.

Figure 3: NAND Flash Memory Trends

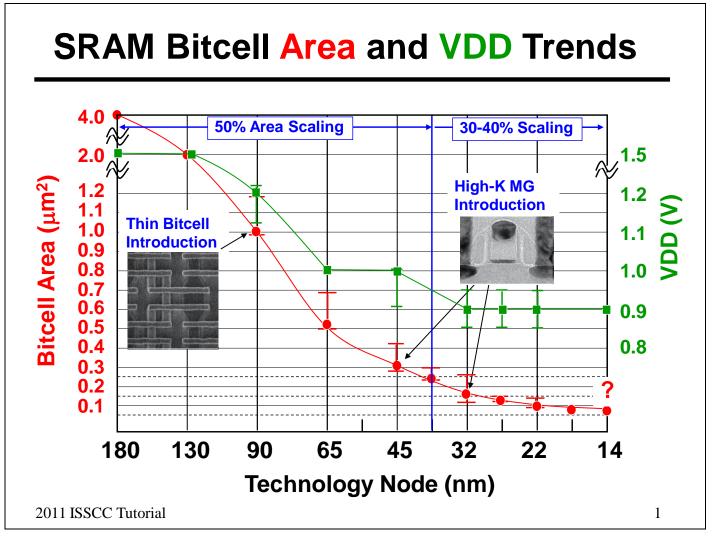

**SRAM Bitcell Design:** Historically, a 50% area reduction in bitcell from node to node has been enabled by the scaling of technology feature size, resulting in a 2x improvement in on-die memory integration with each node reduction and continuing improvements in performance. However, the reduction in transistor geometry is increasing device variability, resulting in a slowdown in the scaling trend as shown in **Figure 4**. Between the 45nm and 32nm technology nodes, bitcell scaling has been reduced to less than the typical 50%. The introduction of High- $\kappa$  Metal Gate technologies at the 45nm node has provided a significant reduction in the equivalent oxide thickness, thereby reducing the V<sub>T</sub> mismatch and allowing further aggressive scaling of device dimensions needed to achieve the scaling of area. However, technology improvements alone are not sufficient to maintain area scaling. SRAM peripheral-circuit-assist features have become the key to maintaining cell stability, readability and write margins, and enable low-voltage operation. New strategies ranging from circuit-level techniques to fundamental changes in array architecture can also enable significant gains in area and power efficiency.

Figure 4: SRAM Bitcell Trends

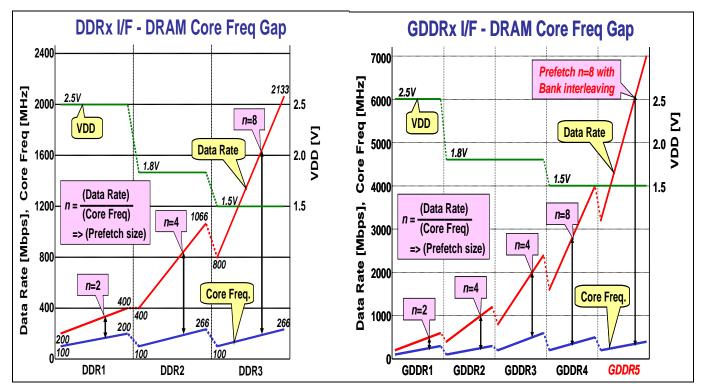

**DRAM & High-Speed I/O:** Unfortunately, the gap between memory-core frequency and external-data rate continues to increase as conventional high-speed wired interface schemes such as DDRx and GDDRx for DRAM and NAND flash memory continue to evolve (**Figure 5**). This leads to the need for a larger prefetch size, which is emerging as a major problem in modern memory systems. However, alternatives which accommodate high data rates through the use of wider or differential interfaces will face the problem of increased pin-counts, and enlarged silicon areas. Combined with 3D integration of memory and memory/logic in near-future commercial products, new interface technologies will yield more memory stacking, along with lower-power and higher-bandwidth interfaces.

Figure 5: DRAM and High-Speed I/O Trends

TRENDS

# RF Subcommittee

## ISSCC 2011 - RF

Subcommittee Chair: Nikolaus Klemmer, Texas Instruments, Dallas, TX Press Designate: Chris Rudell, University of Washington, Seattle, WA

## OVERVIEW

#### CONTEXT AND PRESENT STATE OF THE ART

- Software-defined radios have long been promoted as the next big thing, but so far have not lived up to the hype due to a lack of adequate performance at a reasonable price point. [3.1, 3.2, 3.6, 3.8, 26.6]

- mm-Wave imaging solutions are still in their infancy. New advances in the fundamental-technology building blocks are required to finally open up exciting new application areas in security and healthcare. [16.2, 16.3, 16.5, 16.6, 16.7]

- Existing 801.11n wireless links in the 2.4 and 5GHz bands deliver speeds up to several hundred Mb/s, and efforts are underway to try and push data rates beyond the 1Gb/s barrier, up to 10Gb/s, using ICs in the mm-Wave band. [16.7]

- FMCW radars are an integral part of advanced automobile safety systems today that are becoming widespread throughout the automotive industry. [16.8]

- Existing health-monitoring requires bulky equipment that must be administered in over-crowded hospitals by overworked health care professionals, putting further strain on an already over-burdened system. [16.9, 16.10]

- Power amplifiers in CMOS have been restricted to non-linear switched-based topologies until now. Are the latest CMOS PA implementations ready for linear amplification prime-time? [24.2, 24.4, 24.5]

- Switched-Capacitor (SC) integrator stages have traditionally been limited to baseband frequencies for converter and filter applications. New SC circuit techniques are now being exploited at RF, for PA applications. [24.3]

#### **MOST-SIGNIFICANT PAPERS**

- New AD-PLL techniques remove impunity to interference in radio front ends enabling highly programmable radio front ends used in high-density environments. [3.1, 3.2]

- Radio receiver architecture has come full circle! Broadcom and UCLA will demonstrate the re-emergence of the oldschool super-heterodyne receiver in 65nm with fully-integrated high-Q IF filters, and UCLA will demonstrate that the similarly-aged super-regenerative receiver can be put to good use in a very compact 186GHz low-power imaging application also in 65nm CMOS. **[3.5, 16.10]**

- Revolutionary advancements in fundamental millimeter-wave technology blocks. A variety of industrial and academic researchers deliver innovative techniques that yield revolutionary millimeter-wave building blocks capable of operating at frequencies up to 300GHz. [16.2, 16.3, 16.5, 16.6, 16.7]

- New AD-PLL techniques dramatically enhance range and velocity resolutions of FMCW radars. An FMCW synthesizer radar by Toshiba achieves range and velocity resolutions of 10cm and 1.4km/h respectively thanks to a 2x wider bandwidth and 6x longer modulation period than previously reported solutions. [16.8]

- New radio techniques enable applications in the medical area by providing a very small form factor, low-cost solution for imaging using both UWB techniques and radio imaging in the 183GHz band. [16.9, 16.10]

- First demonstrations of linear PAs in CMOS. Intel and Samsung will deliver CMOS-only linear PA solutions addressing the WLAN and EDGE/GSM markets respectively. [24.2, 24.4]

- Demonstration of switched-capacitor techniques being applied to high-power signal processing. The University of Washington will demonstrate a 2GHz power amplifier delivering 25dBm, using purely switched-capacitor techniques for signal modulation. [24.3]

- Record power levels for a 60GHz PA in 65nm CMOS. UC Berkeley will demonstrate 18.6dBm saturation power using only 0.28mm<sup>2</sup> of silicon area! [24.5]

#### APPLICATIONS AND ECONOMIC IMPACT

- Continued enhancement of all-digital PLLs, and their migration to modern 65nm CMOS processes, will continue to improve sensitivity and reduce interference in wireless and wireline applications. The net result will be low cost solutions with even higher levels of performance. [3.1, 3.2]

- Software-defined radios are a step closer to reality with the newest implementation of broadband high-linearity, harmonic rejecting receivers, and multi-decade frequency synthesizers. [3.6, 3.8, 26.6]

- Millimeter-wave building blocks with frequencies up to 300GHz will play an important role in applications, such as security and 10Gb/s data-rate applications. [16.2, 16.3, 16.5, 16.6, 16.7]

- Improved FMCW radar performance will enable better automobile safety systems, leading to even greater adoption within the industry, which in turn will lower costs for the consumer due to increased product volumes and competitive marketing.

[16.8]

- Patient healthcare monitoring is taken to a whole new level: Your vital signs can be monitored from the next room without

wearing any electronics on your body with this UWB impulse radar in the GHz-range. In addition, extremely low-cost small

form factor tereahertz imaging systems are now within our reach! [16.9, 16.10]

- Linear Power Amplifiers (PA) for 2.5G and 3G are currently the domain of GaAs technology which is expensive, and difficult to integrate into low-cost-handset designs. All-CMOS linear PAs promise lower costs and the possibility of greater levels of integration with other CMOS building blocks in future SoCs. [24.2, 24.4]

- New transmitter and Power Amplifier (PA) design techniques and topologies will substantially increase mobile phone battery life, allowing consumers to run their cell phones for several weeks before requiring a charge. [24.3]

- Achieving high transmission power levels in conventional CMOS will ensure low-cost solutions that can be tightly integrated, thereby enabling the continued adoption of 60GHz wireless technologies. [24.5]

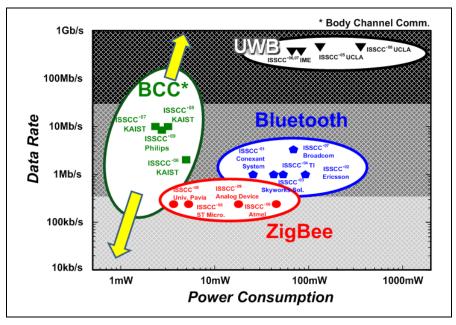

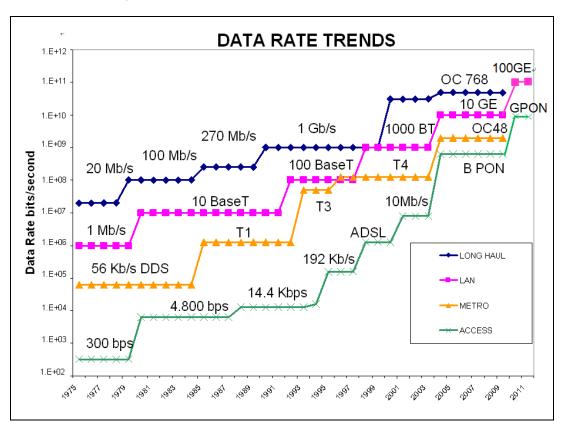

### **TRENDS IN DATACOM TECHNOLOGIES**

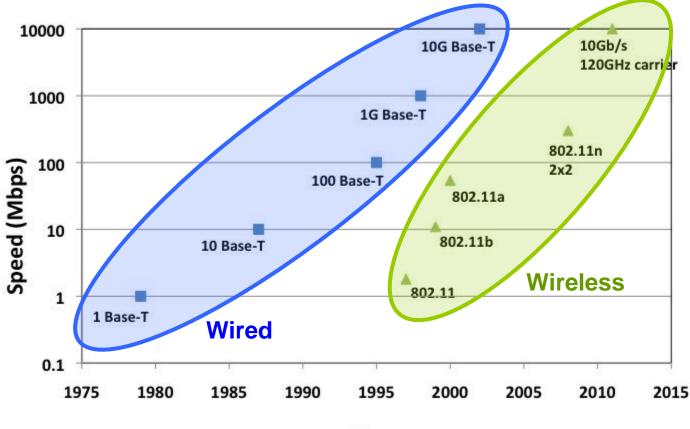

Increasing demand for higher data rates fueled by multimedia applications require communication systems to run at everincreasing speeds. The bandwidth capabilities of wireline and wireless data communication systems are projected in the data-ratetrend chart shown below. As depicted, millimeter-wave frequency bands in the 120GHz range are enabling a new, potentiallydisruptive technology. Using carrier frequencies in the 120GHz band, new wireless transceiver systems allow data rates up to 10Gb/s for short-range wireless data communication. This chart also indicates that wireless links are approaching the data rates traditionally realized with wireline solutions. Advances in wireless-communication data rates are being enabled by advanced nanometer-length CMOS technologies, combined with innovative circuit and radio-architecture implementations.

Data Rate Trend for Wired and Wireless Communication Systems

Year

TRENDS

# TECHNOLOGY DIRECTIONS SUBCOMMITTEE

### **ISSCC 2011 – TECHNOLOGY DIRECTIONS**

**Subcommittee Chair:** Siva Narendra, Tyfone, Portland, OR **Press Designate:** Eugenio Cantatore, Eindhoven University of Technology, Eindhoven, The Netherlands

## OVERVIEW

#### CONTEXT AND PRESENT STATE OF THE ART

- Continuous monitoring of vital health signals will help reduce the cost of healthcare, enable proactive and preventive care, and reduce the need for routine clinical visits. [2.1]

- Sleep apnea is a life-threatening illness that requires bulky sensing systems, making the therapy highly inconvenient. [2.2]