# 2010 PRESS KIT

#### **ISSCC PRESS KIT DISCLAIMER**

The material presented here is preliminary. As of November 1, 2009, there is not enough information to guarantee its correctness. Thus, it must be used with some caution.

## ISSCC VISION STATEMENT

The International Solid-State Circuits Conference is the foremost global forum for presentation of advances in solid-state circuits and systems-on-a-chip. The Conference offers a unique opportunity for engineers working at the cutting edge of IC design and use to maintain technical currency, and to network with leading experts.

## TABLE OF CONTENTS

| CONFERENCE THEME         3           EVENTS         4           PARER STATISTICS         5           PLENARY SESSION         6           TECHNICAL HIGHLIGHTS         9           EDUCATIONAL EVENTS         14           EVENINS         14           EVENINS         14           EVENING SESSIONS         17           ISSCC 2010 - ANALOG         19           OVERVIEW         21           ISSCC 2010 - DATA CONVERTERS         23           OVERVIEW         25           ISSCC 2010 - HIGH PERFORMANCE DIGITAL         27           OVERVIEW         25           ISSCC 2010 - HIGH PERFORMANCE DIGITAL         27           OVERVIEW         23           ISSCC 2010 - IMAGERS, MEMS, MEDICAL AND DISPLAY         35           OVERVIEW         37           TREND ESSAY         39           ISSCC 2010 LOW-POWER DIGITAL         43           OVERVIEW         45           ISSCC 2010 - MEMORY         47           OVERVIEW         57           ISSCC 2010 - MEMORY         57           ISSCC 2010 - PHASE LOCKED LOOPS         55           OVERVIEW         57           ISSCC 2010 - PADIO FREQUENCY                                            | ISSCC 2010 – CONFERENCE OVERVIEW   | 1       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------|

| PAPER STATISTICS       5         PLENARY SESSION       6         TECHNICAL HIGHTIS       9         EDUCATIONAL EVENTS       14         EVENTG SESSIONS       16         SUBCOMMITTEE CONTRIBUTIONS       17         ISSCC 2010 – ANALOG       19         OVERVIEW       21         ISSCC 2010 – DATA CONVERTERS       23         OVERVIEW       25         ISSCC 2010 – HIGH PERFORMANCE DIGITAL       27         OVERVIEW       29         TREND ESSAY       31         TREND CHARTS       32         ISSCC 2010 – HIAGERS, MEMS, MEDICAL AND DISPLAY       35         OVERVIEW       31         TREND ESSAY       39         ISSCC 2010 LOW-POWER DIGITAL       43         OVERVIEW       45         ISSCC 2010 LOW-POWER DIGITAL       43         OVERVIEW       45         ISSCC 2010 LOW-POWER DIGITAL       43         OVERVIEW       57         ISSCC 2010 – MEMORY       47         OVERVIEW       57         ISSCC 2010 – RADIO FREQUENCY       57         OVERVIEW       57         ISSCC 2010 – REDIO FREQUENCY       57         OVERVIEW       57                                                                                                     |                                    |         |

| PIENARY SESSION         6           TECHNICAL HIGHIGHTS         9           EDUCATIONAL EVENTS         14           EVENING SESSIONS         16           SUBCOMMITTEE CONTRIBUTIONS         17           ISSCC 2010 – ANALOG         19           OVERVIEW         21           ISSCC 2010 – DATA CONVERTERS         23           OVERVIEW         25           ISSCC 2010 – HIGH PERFORMANCE DIGITAL         27           OVERVIEW         29           TREND ESSAY         31           TREND CHARTS         32           ISSCC 2010 – IMAGERS, MEMS, MEDICAL AND DISPLAY         35           OVERVIEW         33           ISSCC 2010 – IMAGERS, MEMS, MEDICAL AND DISPLAY         35           OVERVIEW         33           ISSCC 2010 – IMAGERS, MEMS, MEDICAL AND DISPLAY         35           OVERVIEW         43           OVERVIEW         43           OVERVIEW         44           ISSCC 2010 – MEMORY         45           ISSCC 2010 – MEMORY         47           OVERVIEW         57           ISSCC 2010 – PHASE LOCKED LOOPS         55           OVERVIEW         57           ISSCC 2010 – PADIO FREQUENCY         59 <td></td> <td>-</td> |                                    | -       |

| TECHNICAL HIGHUGHUSHTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PAPER STATISTICS                   | 5       |

| EDUCATIONAL EVENTS       14         EVENING SESSIONS       16         SUBCOMMITTEE CONTRIBUTIONS       17         ISSCC 2010 - ANALOG       19         OVERVIEW       21         ISSCC 2010 - DATA CONVERTERS       23         OVERVIEW       25         ISSCC 2010 - HIGH PERFORMANCE DIGITAL       27         OVERVIEW       29         TREND ESSAY       31         TREND ESSAY       31         TREND ESSAYS       32         ISSCC 2010 - IMAGERS, MEMS, MEDICAL AND DISPLAY       35         OVERVIEW       37         TREND ESSAYS       39         ISSCC 2010 LOW-POWER DIGITAL       43         OVERVIEW       45         ISSCC 2010 - MEMORY       47         OVERVIEW       49         TREND ESSAY       51         ISSCC 2010 - PHASE LOCKED LOOPS       55         OVERVIEW       57         ISSCC 2010 - RADIO FREQUENCY       59         OVERVIEW       61         TREND ESSAYS       63         ISSCC 2010 - TECHNOLOGY DIRECTIONS       65         OVERVIEW       71         TREND ESSAYS       63         ISSCC 2010 - WIRELIESS       69                                                                                                       |                                    |         |

| EVENING SESSIONS       16         SUBCOMMITTEE CONTRIBUTIONS       17         ISSCC 2010 – ANALOG       19         OVERVIEW       21         ISSCC 2010 – DATA CONVERTERS       23         OVERVIEW       25         ISSCC 2010 – DATA CONVERTERS       23         OVERVIEW       25         ISSCC 2010 – HIGH PERFORMANCE DIGITAL       27         OVERVIEW       29         TREND ESSAY       31         TREND CHARTS       32         ISSCC 2010 – IMAGERS, MEMS, MEDICAL AND DISPLAY       35         OVERVIEW       37         TREND ESSAYS       39         ISSCC 2010 – MEMORY       43         OVERVIEW       45         ISSCC 2010 – MEMORY       47         OVERVIEW       45         ISSCC 2010 – PHASE LOCKED LOOPS       55         OVERVIEW       57         ISSCC 2010 – PHASE LOCKED LOOPS       55         OVERVIEW       61         TREND ESSAYS       63         ISSCC 2010 – TECHNOLOGY DIRECTIONS       65         OVERVIEW       71         TREND ESSAY       73         ISSCC 2010 – WIRELESS       69         OVERVIEW       71     <                                                                                                     |                                    |         |

| SUBCOMMITTEE CONTRIBUTIONS       17         ISSCC 2010 - ANALOG       19         OVERVIEW       21         ISSCC 2010 - DATA CONVERTERS       23         OVERVIEW       25         ISSCC 2010 - HIGH PERFORMANCE DIGITAL       27         OVERVIEW       29         TREND ESSAY       31         TREND ESSAY       32         ISSCC 2010 - IMAGERS, MEMS, MEDICAL AND DISPLAY       35         OVERVIEW       37         TREND ESSAYS       39         ISSCC 2010 L OW-POWER DIGITAL       43         OVERVIEW       45         ISSCC 2010 - MEMORY       45         ISSCC 2010 - PHASE LOCKED LOOPS       55         OVERVIEW       57         ISSCC 2010 - RADIO FREQUENCY       59         OVERVIEW       61         TREND ESSAYS       63         ISSCC 2010 - TECHNOLOGY DIRECTIONS       65         OVERVIEW       61         TREND ESSAYS       63         ISSCC 2010 - WIRELESS       69         OVERVIEW       71         TREND ESSAYS       63         ISSCC 2010 - WIRELINE       73                                                                                                                                                                   | EDUCATIONAL EVENTS                 | 14      |

| ISSCC 2010 - ANALOG       19         OVERVIEW       21         ISSCC 2010 - DATA CONVERTERS       23         OVERVIEW       25         ISSCC 2010 - HIGH PERFORMANCE DIGITAL       27         OVERVIEW       29         TREND ESSAY       31         TREND CHARTS       32         ISSCC 2010 - IMAGERS, MEMS, MEDICAL AND DISPLAY       35         OVERVIEW       37         TREND ESSAYS       39         ISSCC 2010 LOW-POWER DIGITAL       43         OVERVIEW       47         OVERVIEW       45         ISSCC 2010 - MEMORY       47         OVERVIEW       51         ISSCC 2010 - PHASE LOCKED LOOPS       55         OVERVIEW       57         ISSCC 2010 - PHASE LOCKED LOOPS       55         OVERVIEW       61         TREND ESSAYS       63         ISSCC 2010 - RADIO FREQUENCY       59         OVERVIEW       61         TREND ESSAYS       63         ISSCC 2010 - WIRELESS       69         OVERVIEW       71         TREND ESSAY       73         ISSCC 2010 - WIRELINE       75         OVERVIEW       71                                                                                                                                     | EVENING SESSIONS                   | 16      |

| OVERVIEW.       21         ISSCC 2010 - DATA CONVERTERS       23         OVERVIEW.       25         ISSCC 2010 - HIGH PERFORMANCE DIGITAL.       27         OVERVIEW.       29         TREND ESSAY       31         TREND CHARTS       32         ISSCC 2010 - IMAGERS, MEMS, MEDICAL AND DISPLAY       35         OVERVIEW.       37         TREND ESSAYS       39         ISSCC 2010 LOW-POWER DIGITAL       43         OVERVIEW.       45         ISSCC 2010 - MEMORY.       47         OVERVIEW.       49         TREND ESSAY       51         ISSCC 2010 - PHASE LOCKED LOOPS       55         OVERVIEW.       57         ISSCC 2010 - PHASE LOCKED LOOPS       55         OVERVIEW.       61         TREND ESSAYS       63         ISSCC 2010 - RADIO FREQUENCY       59         OVERVIEW.       61         TREND ESSAYS       63         ISSCC 2010 - WIRELESS       69         OVERVIEW.       71         TREND ESSAYS       63         ISSCC 2010 - WIRELINE       73         ISSCC 2010 - WIRELINE       73                                                                                                                                             | SUBCOMMITTEE CONTRIBUTIONS         | 17      |

| OVERVIEW.       21         ISSCC 2010 - DATA CONVERTERS       23         OVERVIEW.       25         ISSCC 2010 - HIGH PERFORMANCE DIGITAL.       27         OVERVIEW.       29         TREND ESSAY       31         TREND CHARTS       32         ISSCC 2010 - IMAGERS, MEMS, MEDICAL AND DISPLAY       35         OVERVIEW.       37         TREND ESSAYS       39         ISSCC 2010 LOW-POWER DIGITAL       43         OVERVIEW.       45         ISSCC 2010 - MEMORY.       47         OVERVIEW.       49         TREND ESSAY       51         ISSCC 2010 - PHASE LOCKED LOOPS       55         OVERVIEW.       57         ISSCC 2010 - PHASE LOCKED LOOPS       55         OVERVIEW.       61         TREND ESSAYS       63         ISSCC 2010 - RADIO FREQUENCY       59         OVERVIEW.       61         TREND ESSAYS       63         ISSCC 2010 - WIRELESS       69         OVERVIEW.       71         TREND ESSAYS       63         ISSCC 2010 - WIRELINE       73         ISSCC 2010 - WIRELINE       73                                                                                                                                             |                                    |         |

| ISSCC 2010 - DATA CONVERTERS       23         OVERVIEW       25         ISSCC 2010 - HIGH PERFORMANCE DIGITAL       27         OVERVIEW       29         TREND ESSAY       31         TREND CHARTS       32         ISSCC 2010 - IMAGERS, MEMS, MEDICAL AND DISPLAY       35         OVERVIEW       37         TREND ESSAYS       39         ISSCC 2010 LOW-POWER DIGITAL       43         OVERVIEW       45         ISSCC 2010 - MEMORY       47         OVERVIEW       49         TREND ESSAY       51         ISSCC 2010 - MEMORY       49         TREND ESSAY       51         ISSCC 2010 - MEMORY       51         ISSCC 2010 - PHASE LOCKED LOOPS       55         OVERVIEW       57         ISSCC 2010 - TECHNOLOGY DIRECTIONS       63         ISSCC 2010 - TECHNOLOGY DIRECTIONS       65         OVERVIEW       67         ISSCC 2010 - WIRELESS       69         OVERVIEW       73         ISSCC 2010 - WIRELINE       75         OVERVIEW       73                                                                                                                                                                                                    |                                    |         |

| OVERVIEW.         25           ISSCC 2010 - HIGH PERFORMANCE DIGITAL.         27           OVERVIEW.         29           TREND ESSAY         31           TREND CHARTS.         32           ISSCC 2010 - IMAGERS, MEMS, MEDICAL AND DISPLAY.         35           OVERVIEW.         37           TREND ESSAYS.         39           ISSCC 2010 LOW-POWER DIGITAL         43           OVERVIEW.         45           ISSCC 2010 - MEMORY.         47           OVERVIEW.         45           ISSCC 2010 - PHASE LOCKED LOOPS         55           OVERVIEW.         57           ISSCC 2010 - PHASE LOCKED LOOPS         55           OVERVIEW.         57           ISSCC 2010 - RADIO FREQUENCY         59           OVERVIEW.         61           TREND ESSAYS         63           ISSCC 2010 - TECHNOLOGY DIRECTIONS         65           OVERVIEW.         61           TREND ESSAY         61           TREND ESSAY         61           ISSCC 2010 - TECHNOLOGY DIRECTIONS         65           OVERVIEW.         71           TREND ESSAY         73           ISSCC 2010 - WIRELESS         69 <td< td=""><td>OVERVIEW</td><td>21</td></td<>        | OVERVIEW                           | 21      |

| OVERVIEW.         25           ISSCC 2010 - HIGH PERFORMANCE DIGITAL.         27           OVERVIEW.         29           TREND ESSAY         31           TREND CHARTS.         32           ISSCC 2010 - IMAGERS, MEMS, MEDICAL AND DISPLAY.         35           OVERVIEW.         37           TREND ESSAYS.         39           ISSCC 2010 LOW-POWER DIGITAL         43           OVERVIEW.         45           ISSCC 2010 - MEMORY.         47           OVERVIEW.         45           ISSCC 2010 - PHASE LOCKED LOOPS         55           OVERVIEW.         57           ISSCC 2010 - PHASE LOCKED LOOPS         55           OVERVIEW.         57           ISSCC 2010 - RADIO FREQUENCY         59           OVERVIEW.         61           TREND ESSAYS         63           ISSCC 2010 - TECHNOLOGY DIRECTIONS         65           OVERVIEW.         61           TREND ESSAY         61           TREND ESSAY         61           ISSCC 2010 - TECHNOLOGY DIRECTIONS         65           OVERVIEW.         71           TREND ESSAY         73           ISSCC 2010 - WIRELESS         69 <td< th=""><th></th><th><b></b></th></td<>           |                                    | <b></b> |

| ISSCC 2010 - HIGH PERFORMANCE DIGITAL       27         OVERVIEW.       29         TREND ESSAY       31         TREND CHARTS       32         ISSCC 2010 - IMAGERS, MEMS, MEDICAL AND DISPLAY       35         OVERVIEW.       37         TREND ESSAYS       39         ISSCC 2010 LOW-POWER DIGITAL       43         OVERVIEW.       45         ISSCC 2010 - MEMORY.       47         OVERVIEW.       45         ISSCC 2010 - PHASE LOCKED LOOPS       55         OVERVIEW.       57         ISSCC 2010 - RADIO FREQUENCY       59         OVERVIEW.       61         TREND ESSAYS       63         ISSCC 2010 - TECHNOLOGY DIRECTIONS       65         OVERVIEW.       67         ISSCC 2010 - WIRELESS       69         OVERVIEW.       67         ISSCC 2010 - WIRELESS       69         OVERVIEW.       71         TREND ESSAY       73                                                                                                                                                                                                                                                                                                                       |                                    |         |

| OVERVIEW.         29           TREND ESSAY         31           TREND CHARTS         32           ISSCC 2010 - IMAGERS, MEMS, MEDICAL AND DISPLAY         35           OVERVIEW.         37           TREND ESSAYS         39           ISSCC 2010 LOW-POWER DIGITAL         43           OVERVIEW.         45           ISSCC 2010 - MEMORY.         47           OVERVIEW.         49           TREND ESSAY         51           ISSCC 2010 - PHASE LOCKED LOOPS         55           OVERVIEW.         57           ISSCC 2010 - PHASE LOCKED LOOPS         55           OVERVIEW.         61           TREND ESSAYS         63           ISSCC 2010 - RADIO FREQUENCY         59           OVERVIEW.         61           TREND ESSAYS         63           ISSCC 2010 - TECHNOLOGY DIRECTIONS         65           OVERVIEW.         67           ISSCC 2010 - WIRELESS         69           OVERVIEW.         71           TREND ESSAY         73           ISSCC 2010 - WIRELINE         75           OVERVIEW.         71                                                                                                                                 | OVERVIEW                           | 25      |

| OVERVIEW.         29           TREND ESSAY         31           TREND CHARTS         32           ISSCC 2010 - IMAGERS, MEMS, MEDICAL AND DISPLAY         35           OVERVIEW.         37           TREND ESSAYS         39           ISSCC 2010 LOW-POWER DIGITAL         43           OVERVIEW.         45           ISSCC 2010 - MEMORY.         47           OVERVIEW.         49           TREND ESSAY         51           ISSCC 2010 - PHASE LOCKED LOOPS         55           OVERVIEW.         57           ISSCC 2010 - PHASE LOCKED LOOPS         55           OVERVIEW.         61           TREND ESSAYS         63           ISSCC 2010 - RADIO FREQUENCY         59           OVERVIEW.         61           TREND ESSAYS         63           ISSCC 2010 - TECHNOLOGY DIRECTIONS         65           OVERVIEW.         67           ISSCC 2010 - WIRELESS         69           OVERVIEW.         71           TREND ESSAY         73           ISSCC 2010 - WIRELINE         75           OVERVIEW.         71                                                                                                                                 |                                    | 07      |

| TREND ESSAY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                    |         |

| TREND CHARTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                    |         |

| ISSCC 2010 - IMAGERS, MEMS, MEDICAL AND DISPLAY       35         OVERVIEW       37         TREND ESSAYS       39         ISSCC 2010 LOW-POWER DIGITAL       43         OVERVIEW       45         ISSCC 2010 - MEMORY       47         OVERVIEW       49         TREND ESSAY       51         ISSCC 2010 - PHASE LOCKED LOOPS       55         OVERVIEW       57         ISSCC 2010 - RADIO FREQUENCY       59         OVERVIEW       61         TREND ESSAYS       63         ISSCC 2010 - TECHNOLOGY DIRECTIONS       65         OVERVIEW       67         ISSCC 2010 - WIRELESS       69         OVERVIEW       71         TREND ESSAYS       73         ISSCC 2010 - WIRELESS       69         OVERVIEW       71         TREND ESSAY       73                                                                                                                                                                                                                                                                                                                                                                                                                  |                                    | -       |

| OVERVIEW.       37         TREND ESSAYS       39         ISSCC 2010 LOW-POWER DIGITAL       43         OVERVIEW.       45         ISSCC 2010 – MEMORY.       47         OVERVIEW.       49         TREND ESSAY       51         ISSCC 2010 – PHASE LOCKED LOOPS       55         OVERVIEW.       57         ISSCC 2010 – RADIO FREQUENCY       59         OVERVIEW.       61         TREND ESSAYS       63         ISSCC 2010 – TECHNOLOGY DIRECTIONS.       65         OVERVIEW.       61         TREND ESSAY       63         ISSCC 2010 – WIRELESS       69         OVERVIEW.       71         TREND ESSAY       73         ISSCC 2010 – WIRELINE       75         OVERVIEW.       71                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | TREND CHARTS                       | 32      |

| OVERVIEW.       37         TREND ESSAYS       39         ISSCC 2010 LOW-POWER DIGITAL       43         OVERVIEW.       45         ISSCC 2010 – MEMORY.       47         OVERVIEW.       49         TREND ESSAY       51         ISSCC 2010 – PHASE LOCKED LOOPS       55         OVERVIEW.       57         ISSCC 2010 – RADIO FREQUENCY       59         OVERVIEW.       61         TREND ESSAYS       63         ISSCC 2010 – TECHNOLOGY DIRECTIONS.       65         OVERVIEW.       61         TREND ESSAY       63         ISSCC 2010 – WIRELESS       69         OVERVIEW.       71         TREND ESSAY       73         ISSCC 2010 – WIRELINE       75         OVERVIEW.       71                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                    | 25      |

| TREND ESSAYS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                    |         |

| ISSCC 2010 LOW-POWER DIGITAL       43         OVERVIEW       45         ISSCC 2010 - MEMORY       47         OVERVIEW       49         TREND ESSAY       51         ISSCC 2010 - PHASE LOCKED LOOPS       55         OVERVIEW       57         ISSCC 2010 - RADIO FREQUENCY       59         OVERVIEW       61         TREND ESSAYS       63         ISSCC 2010 - TECHNOLOGY DIRECTIONS       65         OVERVIEW       67         ISSCC 2010 - WIRELESS       69         OVERVIEW       71         TREND ESSAY       73         ISSCC 2010 - WIRELINE       75         OVERVIEW       75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                    |         |

| OVERVIEW.       45         ISSCC 2010 - MEMORY.       47         OVERVIEW.       49         TREND ESSAY.       51         ISSCC 2010 - PHASE LOCKED LOOPS       55         OVERVIEW.       57         ISSCC 2010 - RADIO FREQUENCY       59         OVERVIEW.       61         TREND ESSAYS       63         ISSCC 2010 - TECHNOLOGY DIRECTIONS.       65         OVERVIEW.       67         ISSCC 2010 - WIRELESS       69         OVERVIEW.       71         TREND ESSAY       73         ISSCC 2010 - WIRELINE       75         OVERVIEW.       71         TREND ESSAY       73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IREND ESSAYS                       | 39      |

| OVERVIEW       45         ISSCC 2010 - MEMORY       47         OVERVIEW       49         TREND ESSAY       51         ISSCC 2010 - PHASE LOCKED LOOPS       55         OVERVIEW       57         ISSCC 2010 - RADIO FREQUENCY       59         OVERVIEW       61         TREND ESSAYS       63         ISSCC 2010 - TECHNOLOGY DIRECTIONS       65         OVERVIEW       67         ISSCC 2010 - WIRELESS       69         OVERVIEW       71         TREND ESSAY       73         ISSCC 2010 - WIRELINE       75         OVERVIEW       71         TREND ESSAY       73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                    | 12      |

| ISSCC 2010 - MEMORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                    |         |

| OVERVIEW       49         TREND ESSAY       51         ISSCC 2010 – PHASE LOCKED LOOPS       55         OVERVIEW       57         ISSCC 2010 – RADIO FREQUENCY       59         OVERVIEW       61         TREND ESSAYS       63         ISSCC 2010 – TECHNOLOGY DIRECTIONS       65         OVERVIEW       67         ISSCC 2010 – WIRELESS       69         OVERVIEW       71         TREND ESSAY       73         ISSCC 2010 – WIRELINE       75         OVERVIEW       77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | UVERVIEW                           | 45      |

| OVERVIEW       49         TREND ESSAY       51         ISSCC 2010 – PHASE LOCKED LOOPS       55         OVERVIEW       57         ISSCC 2010 – RADIO FREQUENCY       59         OVERVIEW       61         TREND ESSAYS       63         ISSCC 2010 – TECHNOLOGY DIRECTIONS       65         OVERVIEW       67         ISSCC 2010 – WIRELESS       69         OVERVIEW       71         TREND ESSAY       73         ISSCC 2010 – WIRELINE       75         OVERVIEW       77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                    | 17      |

| TREND ESSAY       51         ISSCC 2010 – PHASE LOCKED LOOPS       55         OVERVIEW       57         ISSCC 2010 – RADIO FREQUENCY       59         OVERVIEW       61         TREND ESSAYS       63         ISSCC 2010 – TECHNOLOGY DIRECTIONS       65         OVERVIEW       67         ISSCC 2010 – WIRELESS       69         OVERVIEW       71         TREND ESSAY       73         ISSCC 2010 – WIRELINE       75         OVERVIEW       77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                    |         |

| ISSCC 2010 - PHASE LOCKED LOOPS       55         OVERVIEW       57         ISSCC 2010 - RADIO FREQUENCY       59         OVERVIEW       61         TREND ESSAYS       63         ISSCC 2010 - TECHNOLOGY DIRECTIONS       65         OVERVIEW       67         ISSCC 2010 - WIRELESS       69         OVERVIEW       71         TREND ESSAY       73         ISSCC 2010 - WIRELINE       75         OVERVIEW       77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                    | -       |

| OVERVIEW.       .57         ISSCC 2010 - RADIO FREQUENCY       .59         OVERVIEW.       .61         TREND ESSAYS       .63         ISSCC 2010 - TECHNOLOGY DIRECTIONS.       .65         OVERVIEW.       .67         ISSCC 2010 - WIRELESS       .69         OVERVIEW.       .71         TREND ESSAY       .73         ISSCC 2010 - WIRELINE       .75         OVERVIEW.       .77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | IREND ESSAT                        |         |

| OVERVIEW.       57         ISSCC 2010 - RADIO FREQUENCY       59         OVERVIEW.       61         TREND ESSAYS       63         ISSCC 2010 - TECHNOLOGY DIRECTIONS.       65         OVERVIEW.       67         ISSCC 2010 - WIRELESS       69         OVERVIEW.       71         TREND ESSAY       73         ISSCC 2010 - WIRELINE       75         OVERVIEW.       77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                    | 55      |

| ISSCC 2010 - RADIO FREQUENCY       59         OVERVIEW       61         TREND ESSAYS       63         ISSCC 2010 - TECHNOLOGY DIRECTIONS       65         OVERVIEW       67         ISSCC 2010 - WIRELESS       69         OVERVIEW       71         TREND ESSAY       73         ISSCC 2010 - WIRELINE       75         OVERVIEW       77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                    |         |

| OVERVIEW.       61         TREND ESSAYS       63         ISSCC 2010 – TECHNOLOGY DIRECTIONS.       65         OVERVIEW.       67         ISSCC 2010 – WIRELESS       69         OVERVIEW.       71         TREND ESSAY       73         ISSCC 2010 – WIRELINE       75         OVERVIEW.       77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | UVERVIEW                           |         |

| OVERVIEW.       61         TREND ESSAYS       63         ISSCC 2010 – TECHNOLOGY DIRECTIONS.       65         OVERVIEW.       67         ISSCC 2010 – WIRELESS       69         OVERVIEW.       71         TREND ESSAY       73         ISSCC 2010 – WIRELINE       75         OVERVIEW.       77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ISSCC 2010 - RADIO ERECHENCY       | 50      |

| TREND ESSAYS       63         ISSCC 2010 – TECHNOLOGY DIRECTIONS       65         OVERVIEW       67         ISSCC 2010 – WIRELESS       69         OVERVIEW       71         TREND ESSAY       73         ISSCC 2010 – WIRELINE       75         OVERVIEW       77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                    |         |

| ISSCC 2010 – TECHNOLOGY DIRECTIONS.       65         OVERVIEW.       67         ISSCC 2010 – WIRELESS.       69         OVERVIEW.       71         TREND ESSAY.       73         ISSCC 2010 – WIRELINE       75         OVERVIEW.       77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                    |         |

| OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | TREND ESSATS                       | 05      |

| OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ISSCC 2010 - TECHNOLOGY DIRECTIONS | 65      |

| ISSCC 2010 – WIRELESS       69         OVERVIEW       71         TREND ESSAY       73         ISSCC 2010 – WIRELINE       75         OVERVIEW       77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                    |         |

| OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                    |         |

| OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ISSCC 2010 – WIRELESS              | . 69    |

| TREND ESSAY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                    |         |

| <b>ISSCC 2010 – WIRELINE</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                    |         |

| OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                    |         |

| OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ISSCC 2010 – WIRFLINF              | . 75    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                    |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                    |         |

| ISSCC 2010 – PRESS-RELEASE SESSION OVERVIEWS |  |

|----------------------------------------------|--|

| CONDITIONS OF PUBLICATION                    |  |

| SESSION OVERVIEWS                            |  |

| ISSCC 2010 – PRESS COPY MATERIALS            |  |

| CONDITIONS OF PUBLICATION                    |  |

| TABLE OF FEATURED PAPERS                     |  |

| PRESS COPY                                   |  |

| ISSCC 2010 – CONTACT INFORMATION             |  |

| TECHNICAL EXPERTS                            |  |

| GENERAL CONTACTS                             |  |

|                                              |  |

## ISSCC 2010 Conference Overview

$\ensuremath{\mathbb{C}}$  Copyright 2009 ISSCC – Do Not Reproduce Without Permission - 2 -

### **CONFERENCE THEME**

### Sensing the Future

#### The ISSCC 2010 Conference theme is:

#### "Sensing the Future"

Magnetic, mechanical, chemical, light, temperature, bio and many other sensors are becoming a natural part of the semiconductor business. Sensors already play a key role in electronics for medical and life sciences. Now, sensors are becoming an integral part of digital systems which measure operating conditions and cope with device variability. In the near future, silicon sensors will be everywhere, not only within electronic products and gadgets, but even inside the human body! Contributions are encouraged from researchers and designers demonstrating novel sensing circuit applications and systems, or circuit and system design in subject areas including, but not limited to the following: digital and analog circuits, memory, imagers, wireless, and wireline communication circuits.

## **EVENTS**

#### TUTORIALS (SUNDAY, FEBRUARY 7, 2010)

9 90-minute Tutorials, each taught twice, by circuit experts from the International Technical Program Committee, serve to meet attendees` needs for introductory material in circuit specialties.

#### FORUMS (SUNDAY, FEBRUARY 7, 2010)

• Circuit experts exchange information on their current research in an all-day informal environment.

SPECIAL-TOPIC EVENING SESSIONS (SUNDAY – TUESDAY, FEBRUARY 7-9, 2010)

- 5 Special-topic presentations, in which experts provide insight and background on a subject of current importance.

- Student Research Preview short student presentations of work-in-progress at Universities around the world.

#### EVENING PANELS (MONDAY - TUESDAY, FEBRUARY 8-9, 2010)

• 2 Panels in which industrial and academic experts debate a selected topic and field audience questions in a semi-formal atmosphere.

TECHNICAL SESSIONS (MONDAY – WEDNESDAY, FEBRUARY 8-10, 2010)

- 4 invited talks presented in the Plenary Session.

- 210 technical papers presented in 25 Regular Sessions, highlighting the latest circuit developments.

#### SOCIAL HOURS (MONDAY - TUESDAY, FEBRUARY 8-9, 2010)

• Network with experts in a wide range of circuit specialties; meet colleagues in an informal exchange; browse the technicalbook exhibits!

#### SHORT COURSE (THURSDAY, FEBRUARY 11, 2010)

• Intensive all-day course on a single topic, taught by world-class instructors, can serve to "jump start" a change in an engineer's circuit specialty.

#### FORUMS (THURSDAY, FEBRUARY 11, 2010)

• Circuit experts exchange information on their current research in an all-day informal environment.

## PAPER STATISTICS

### OVERALL:

- 4 papers invited

- 638 papers submitted to ISSCC 2010

- 210 papers accepted

- 85 papers from North America, including

- 42 Industry papers

- 43 University papers

- 66 papers from the Far East, including

- 38 Industry papers

- 28 University papers

- 59 papers from Europe, including

- 28 Industry papers

- 31 University papers

- 27 Sessions, over 3 days

| INTERNATIONAL SCOPE:                  | <u>2010</u> | <u>2009</u> | <u>2008</u> | <u>2007</u> |

|---------------------------------------|-------------|-------------|-------------|-------------|

| Americas:                             | 41 %        | 38 %        | 43 %        | 39 %        |

| Far East:                             | 31 %        | 35 %        | 28 %        | 31 %        |

| Europe:                               | 28 %        | 27 %        | 29 %        | 30%         |

| WIDE COVERAGE:                        | <u>2010</u> | <u>2009</u> | <u>2008</u> | <u>2007</u> |

| Analog:                               | 9 %         | 11 %        | 9 %         | 7 %         |

| Data Converters:                      | 7 %         | 7 %         | 10 %        | 7 %         |

| High-Performance Digital:             | 10%         | 4 %         | 7 %         | 13%         |

| Imagers, MEMs, Medical, and Displays: | 12 %        | 12 %        | 11 %        | 12%         |

| Low-Power Digital:                    | 6 %         | 6 %         | 5 %         | 4%          |

| Memory:                               | 11 %        | 9 %         | 12 %        | 8%          |

| PLL:                                  | 6 %         |             |             |             |

| RF:                                   | 8 %         | 11 %        | 11 %        | 10%         |

| Technology Directions:                | 12 %        | 13 %        | 12 %        | 12%         |

| Wireless:                             | 11 %        | 13 %        | 11 %        | 12%         |

| Wireline:                             | 8 %         | 14 %        | 11 %        | 13%         |

© Copyright 2009 ISSCC – Do Not Reproduce Without Permission

## PLENARY SESSION

#### Paper 1.1:

#### **MEMS for Automotive and Consumer Applications**

Jiri Marek, Senior Vice President, Robert Bosch, Reutlingen, Germany

- MEMS sensors are increasingly more important and even common place.

- MEMS-assisted electronic systems are making system reactions to human needs more intelligent, and much faster than unaided humans can provide.

- MEMS success has been based on their reducing size, reducing power and reducing cost.

- MEMS development, thus far, has relied on surface micromachining whose development was the breakthrough required for this advance.

- MEMS success relied as well on innovative ASIC design, simulation of electrical and mechanical behaviour, and deep understanding of package and structure over temperature and lifetime.

- Bosh has evolved these capabilities over 20 years and over 1 billion sensors.

- Earliest MEMS successes were in airbag control and gyroscopes for vehicle-dynamics control.

- Now, consumer applications abound: switching the cell-phone from portrait to landscape as the phone orientation changes, avoiding disk damage as the laptop falls, identifying vehicle vertical location in parking and multi-level highway structures through pressure sensing, detecting weather trends, measuring personal altitude, monitoring activity in shoes and sportswear, and providing intuitive controls for games and other interfaces.

- This presentation will consider other applications such as inkjet heads and micromirrors, as well as the challenges to be faced by MEMS-creating technologies.

- Bosh product evolution will be described up to current designs for inertial sensors that are critical to so-called "ESP®-systems".

- Arising new applications, such as energy harvesters and micro-fuel-cells will be discussed.

#### Paper 1.2:

#### Harnessing Technology to Advance the Next-Generation Mobile User-Experience

Greg Delagi, Senior Vice President, Texas Instruments, Dallas, TX

- The mobile handset market is driven by increased bandwidth, increased processing performance, improved screen technology and reducing power consumption.

- Current 3G/4G handsets are multimedia Internet devices, with big screens, HD video, gaming, HD camcorders, controlled by touch screens in a myriad of social, entertainment, and productivity applications.

- The mobile future portends new modes of social interaction.

- Handsets of the future will be smart autonomous lifestyle devices with a multitude of incorporated sensors, applications and display options, all designed to make life easier and more productive!

- Future displays including 3D imaging, virtual interaction and conferencing will make every call feel like you are right there, providing an experience far beyond today's lesser technologies.

- 3D touch screen with image projection and gesturing will support a new era of intuitive mobile-device applications, interaction, and information sharing.

- True mobile companions will require new compelling services and features to function as well as the office or home computer.

- The massive amounts of data needed by the mobile companion will require immense improvements in system performance, including specialized circuits, highly-parallel architectures, and new packaging design.

- A smart-mobile-companion device will seem to be always-on always-aware in a way that is completely seamless and transparent, by automatically determining the best and most appropriate modem link, whether WiFi, LTE, 5G, or mmWave, based on which will optimize performance, battery life, and costs to deliver the best-possible user experience.

- Future systems will require today's modem technologies, along with new man-machine interfaces and body-areanetworks.

- Additional energy supply needed by computational requirements necessitates improved energy efficiency, particularly to deliver all-day operation or two-day always-on standby without a recharge.

- Innovations ranging from low-voltage digital and analog circuits, non-volatile memory, and adaptive power management, to energy harvesting, will be needed to extend battery life to a week or more.

- Increased bandwidth, combined with decreased latency, lower power requirements combined with energy scavenging and harvesting, massive multimedia processing power, and new interface technologies will all work together, will revolutionize how we interact with our smart-companions of the future.

- The implementation challenges will be met with strong collaboration in research and development by universities, government agencies, and corporations, with smart mobile-companion devices likely to be a reality within 10 years!

#### Paper 1.3:

#### Challenges of Image Sensor Development

Tomoyuki Suzuki, Senior Vice President, Sony, Atsugi, Kanagawa, Japan

- The semiconductor industry has been pushed by successes in digitalization and computerization. And now, is further encouraged by successes in networking.

- Image digitalization has been an important part of these successes.

- Currently, and in the future, image sensors have been, and will remain, key elements in these developments.

- Digital cameras were initiated in 1969 by the invention at Bell Laboratories of CCD image sensors, (for which the Nobel Prize was granted in 2009), and extended by them and others through the mid 1970s, leading to the first video cameras in the mid-1980s.

- Still camera use expanded into the 21<sup>st</sup> century, with high resolution capability increasingly demonstrated, leading in 2005 to an HD digital video camera which was able to record a 1080i high-definition image using CMOS image sensors!

- As CMOS image sensors achieve higher performance and higher speed, the use of CMOS-equipped D-SLR and cell-phone cameras is expanding.

- Over the past 25 years, camera size has decreased by a factor of 500, as a result of pixel miniaturization, with image-sensor photosensitivity improving by ten-fold per decade.

- These advances were brought about by the use of an n-type substrate to reduce pixel size, and to implement electronic-shutter function, as well as, a Tungsten light shield to reduce the smear signal to -100dB for a pixel size of 3.9µm. Such developments led to the 2M pixel digital still camera in 1999.

- Beginning in 1998, high-speed imaging development at Sony emphasizing increased read-out speed through parallelism, led to the 10M pixel CMOS image sensor providing more than 70dB dynamic range with a high-speed read-out of 576M pixels/s.

- This imager which can also be operated with a 16:9 aspect ratio in a 6M pixel mode at 60 frames/s, utilizes column ADCs, and a back-illuminated structure. This design is currently impacting digital still and video cameras, and will dominate the cell-phone market in the future.

- The presentation will include milestones in the development of the CMOS image sensor such as "3D", "4Kx2K", "global shutter", and describe new materials, new structures, and new processes to be employed.

#### Paper 1.4:

#### Nanoelectronics in Retrospect, Prospect, and Principle

James Meindl, Professor, Georgia Institute of Technology, Atlanta, GA

- The information revolution has been the paramount economic development of the past five decades.

- Principal driver of the information revolution has been silicon microchip technology, which has advanced in productivity by a factor of approximately one billion and in performance by a factor of nearly one million (for microprocessor chips, for example).

- Productivity has advanced, top-down, through directed assembly with scaling to 25nm, and, bottom-up, through self-assembly nanotechnology to 300mm single-crystal silicon ingots.

- While scaling maintains IGFET dynamic power-delay product, gate-tunneling current, subthreshold channel leakage, manufacturing tolerances, interconnect latency with copper size effects, become problematic.

- Solutions include: Increased chip I/O, improved heat removal, and 3D chip stacking.

- For the perceived saturation of the advance of silicon technology early in the 2020s, a new genre of nanoelectronics is needed.

- The leading candidate is graphene, with its ballistic carrier transport, adjustable energy band gap of nanoribbons, amenability to both top-down and bottom-up processes, and the potential for 3D monolithic integration. However, graphene still lacks the equivalent of the "transistor" and of the "integrated circuit".

## TECHNICAL HIGHLIGHTS

#### Analog:

- A completely new type of integrated frequency reference uses silicon thermal time constants to achieve excellent accuracy over the full commercial temperature range. An accuracy of ±0.2% is achieved without trimming! [4.1]

- New techniques and meticulous implementations are used to drive down offset and noise in CMOS instrumentation amplifiers. Fully integrated chopper amplifiers achieve 2μV offsets with μW power consumption. [4.2, 4.4]

- Audio-driver designs operate in class D and class G using nanometer geometries. With 79% efficiency and 100dB SNR achieved, using 45nm CMOS, even nanometer SoC applications can include high-quality speaker-driver functions. [4.6, 4.7]

- Analog control is being replaced by digital signal processing in advanced DC/DC power supplies. Clever control techniques enable several outputs to be generated with a single inductor, reducing external component count and cost.

[10.3, 10.5, 10.6]

- Nanometer technology makes charge pumps viable for delivering significant power levels. A switched-capacitor converter in 32nm CMOS can deliver over half a Watt per mm<sup>2</sup>. **[10.8]**

#### Data Converters:

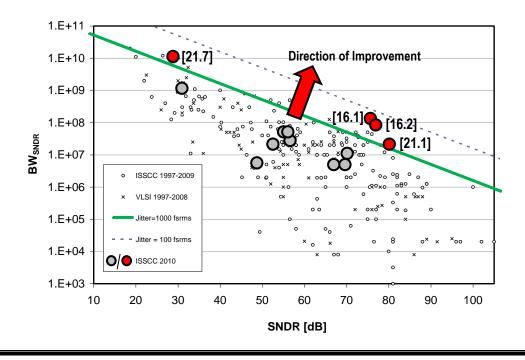

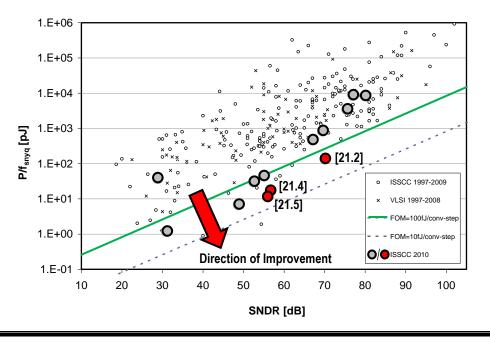

- Breaking the 100dB linearity barrier at sample rate of more than 100MS/s enables multi-carrier GSM base-stations. [16.1, 16.2]

- The first 45nm CMOS high-performance audio ADC achieves 110dB Signal-to-Noise Ratio (SNR) at only 500µW in 0.04mm<sup>2</sup>. [16.7]

- Unparalleled speed of a new ADC impacts medical devices. Its 12.5MS/s operation with 18-bit resolution, reduces power and complexity for MRI and digital X-ray.[21.1]

- A record breaking 40GS/s sample rate is demonstrated in a mainstream 65nm CMOS process. [21.7]

#### **High-Performance Digital:**

- The next processor generation reaches unprecedented integration levels using devices comprised of just a handful of atoms. Both Intel and AMD present designs that use Hi-κ metal-gate 32nm manufacturing processes that yield 50% greater integration in the same area with the same power, as the previous generation. [5.1, 5.6]

- The amount of computational parallelism integrated in the next generation of server processors has been taken to new extremes. SUN has integrated 128 threads per chip, enabling 128 applications to run simultaneously with a whopping 2.4 Tb/s of I/O bandwidth. This leading edge processor is built in 40nm technology, has 16 cores with 8 threads each, and a 6MB L2 cache. [5.2]

- New devices are being integrated to enable the continued performance growth of processor designs. IBM presents a high-end processor that uses embebbed DRAM (eDRAM) memory technology which is over 3 times as dense as the conventional SRAM used in other commercial processors. The 567mm<sup>2</sup> 45nm chip includes 32MB of integrated memory, 1.2B transistors, and has 8 cores with 4 threads each which will enable the most demanding high-end server applications.

[5.4]

- As technology shrinks, small transistors having only a few atoms in critical parts, exhibit large variations, necessitating innovative techniques for reliable integration in the billions. This year, at ISSCC, three presentations address innovations

regarding on-die-aging and path-delay monitoring with extremely fine resolution sensing and adaptation capabilities. [9.7, 9.8, 9.10]

#### Imagers, MEMS, Medical and Displays (IMMD):

- Increased lifetime displays are closer to reality! A new stable RGBW AMOLED display with OLED degradation compensation substantially reduces image sticking and increases the useful lifetime of active OLED displays. [6.3]

- A signal processor with the lowest-reported power consumption extracts the heart's rhythm with elegant simplicity. This circuit consumes only 30µW, enabling it to run off a small battery for months, constantly monitoring the state of the patient for the diagnosis of chronic illness. [6.6]

- Integrated temperature sensors needing no calibration can be used anywhere and everywhere! Quality is not sacrificed with ±0.2°C 3σ accuracy from –55°C to 125°C. [17.4]

- A new Aluminum-Nitride-on-silicon resonator is an important step towards integrating high-Q, low-phase-noise reference oscillators on-chip. The associated transimpedance amplifier has a gain >76dB-Ohm across a bandwidth of 2.5GHz, with a figure-of-merit of 2190GHz·Ω/mW, with a 500fF load. [17.6]

- Time-of-flight sensor with the smallest pixel enables the first generation of range-finding sensors for gaming applications. Integrated optical sensors and interfaces provides an 80×60 pixel range-finding image sensor with 10×10 µm<sup>2</sup> lock-in pixels. [22.7]

- The first backside-illuminated (BSI) CMOS image sensor with 10Mpixel resolution opens new avenues. A BSI sensor with 1/2.3-inch 10.3 Mpixel image using 1.65×1.65µm<sup>2</sup> pixels, operates up to 50 frames per second and achieves a sensitivity of 9890e-/lux·s. [22.9]

#### Low-Power Digital:

- The first functional 4G silicon chips are described enabling high-speed communication for netbooks, smart phones, and the next generation of mobile devices. ETH Zurich with Advanced Circuit Pursuit and CEA-LETI with T. U. Kaiserslautern describe chips that implement 390 Mb/s turbo code decoding, and a multimode software-defined radio capable of 4G, WIMAX, 802.11n, and cognitive radio. **[15.1, 15.3]**

- Low-power processors break through the gigahertz barrier, enabling a new generation of smart phones with never-beforeseen capabilities. ARM and Intel describe new embedded processors with over 1GHz operation at power levels under 50 mW, while Qualcomm describes low-power-design techniques used in their 1.4GHz Snapdragon processor. [15.5, 15.6, 15.7]

- The first super-HD and 3D-video decoder is presented. This 90nm chip supports video signals with 4096x2160 resolution or multiview video, consuming only 59mW. [18.3]

- A massively parallel processor enables advanced intelligent image processing for surveillance cameras and multimedia phones. With 2048 cores, this chip can be applied to object tracking, face/gesture detection, and other computationally intensive image processing problems. **[18.5]**

#### Memory:

- Highest density of 64Mb STT-MRAM with smallest perpendicular cell of 0.358µm<sup>2</sup> in 65nm CMOS. The 30ns access time is used a clamped reference with a new adequate-reference-based sensing schemes. [14.2]

- Highest density of 64Mb CMOx memory in 0.13μm CMOS in a four-layer 0.17μm<sup>2</sup> cross-point-cell array. Using the multilayer capability, this memory is scalable to 64Gb capacity. [14.3]

- Fastest 12ns 4Mb embedded PCM in 90nm CMOS ever reported! Fast read is achieved by using low-voltage MOS in the hierarchical column decoder. [14.7]

- Highest density of 1Gb PCM on 45nm CMOS with 1.8V operation features the fastest-ever read/write performance with 266MB/s and 9MB/s read/write throughputs respectively. **[14.8]**