# ISSCC VISION STATEMENT

The International Solid-State Circuits Conference is the foremost global forum for presentation of advances in solid-state circuits and systems-on-a-chip. The Conference offers a unique opportunity for engineers working at the cutting edge of IC design and use to maintain technical currency, and to network with leading experts.

# TABLE OF CONTENTS

| ACTUVITIES AT ISSOCT 2009<br>ACTIVITIES AT ISSOCT 2009<br>CONFERENCE THEME<br>4 SIGNIFICANT RESULTS<br>ISSCC 2009 - CONFERENCE OVERVIEW<br>9<br>EVENTS<br>11<br>PAPER STATISTICS<br>12<br>PIELAVARY SESSION<br>13<br>TECHNICAL HIGHLIGHTS<br>14<br>PAPER STATISTICS<br>12<br>PIELAVARY SESSION<br>13<br>TECHNICAL HIGHLIGHTS<br>14<br>PAPER STATISTICS<br>14<br>PIELAVARY SESSION<br>15<br>TECHNICAL HIGHLIGHTS<br>15<br>EVENTS<br>15<br>SUDENT FORUM<br>12<br>STUDENT FORUM<br>12<br>STUDENT FORUM<br>12<br>SSCC 2009 - ANALOG<br>23<br>OVERVIEW<br>15<br>FOREWARNED IS FOUR-ARMED; CLASSIC ANALOG MISTEAKS TO AVOID<br>29<br>Tantorial<br>15<br>SSCC 2009 - DATA CONVERTERS<br>30<br>OVERVIEW<br>15<br>FOREWARNED IS FOUR-ARMED; CLASSIC ANALOG MISTEAKS TO AVOID<br>29<br>Tantorial<br>15<br>SSCC 2009 - DATA CONVERTERS<br>30<br>OVERVIEW<br>15<br>FOREWARNED SAFADOS<br>31<br>SSCC 2009 - HIGH PERFORMANCE DIGITAL<br>33<br>OVERVIEW<br>45<br>FORUM CLOCK SYNTHESIS DESIGN<br>41<br>ISSCC 2009 - HIGH PERFORMANCE DIGITAL<br>33<br>OVERVIEW<br>45<br>FORUM MULTI-DOMAIN PROCESSORS<br>49<br>FORUM<br>45<br>FORUM MULTI-DOMAIN PROCESSORS<br>49<br>FORUM MULTI-DOMAIN PROCESSORS<br>49<br>FORUM MULTI-DOMAIN PROCESSORS<br>49<br>FORUM MULTI-DOMAIN PROCESSORS<br>49<br>FORUM MULTI-DOMAIN PROCESSORS<br>49<br>FORUM MULTI-DOMAIN PROCESSORS<br>40<br>FORUM MULTI-DOMAIN PROCESSORS | 17221 | 2000 - EXECI         | JTIVE SUMMARY                                              | 1  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------|------------------------------------------------------------|----|

| CONFERENCE THEME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10000 |                      |                                                            |    |

| SIGNIFICANT RESULTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |                      |                                                            |    |

| ISSCC 2009 - CONFERENCE OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |                      |                                                            |    |

| EVENTS.       11         PAPER STATISTICS.       12         PLENARY SESSION       13         TECHNICAL HIGHLIGHTS       15         EVENTS.       19         Stort Course.       20         Tutorials       21         STUDENT FORUM.       21         STUDENT FORUM.       22         ISSCC 2009 - ANALOG       33         OVERVIEW.       25         FATURED PAPERS.       26         Panel       FOREWARNED IS FOUR-ARMED; CLASSIC ANALOG MISTEAKS TO AVOID.         9       Tutorial       CONTINUOUS-TIME FILTERS.         9       Tutorial       CONTINUOUS-TIME FILTERS.         9       70       33         0VERVIEW.       35         FORUMED PAPERS.       33         0VERVIEW.       35         FEATURED PAPERS.       33         0VERVIEW       35         FEATURED PAPERS.       36         Tutorial       SAR ADCS       39         OVERVIEW       35         FEATURED PAPERS.       36         11       ISSCC 2009 - HIGH PERFORMANCE DIGITAL       43         OVERVIEW       45         FEATURED PAPERS.       50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       | SIGNIFICANT NESO     |                                                            |    |

| EVENTS.       11         PAPER STATISTICS.       12         PLENARY SESSION       13         TECHNICAL HIGHLIGHTS       15         EVENTS.       19         Stort Course.       20         Tutorials       21         STUDENT FORUM.       21         STUDENT FORUM.       22         ISSCC 2009 - ANALOG       33         OVERVIEW.       25         FATURED PAPERS.       26         Panel       FOREWARNED IS FOUR-ARMED; CLASSIC ANALOG MISTEAKS TO AVOID.         9       Tutorial       CONTINUOUS-TIME FILTERS.         9       Tutorial       CONTINUOUS-TIME FILTERS.         9       70       33         0VERVIEW.       35         FORUMED PAPERS.       33         0VERVIEW.       35         FEATURED PAPERS.       33         0VERVIEW       35         FEATURED PAPERS.       36         Tutorial       SAR ADCS       39         OVERVIEW       35         FEATURED PAPERS.       36         11       ISSCC 2009 - HIGH PERFORMANCE DIGITAL       43         OVERVIEW       45         FEATURED PAPERS.       50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12221 | 2000 - CONF          |                                                            | 0  |

| PAPER STATISTICS.       12         PLENARY SESSION       13         TECHNICAL HIGHLIGHTS       15         EVENING SESSIONS       19         Short Course.       20         Tutorials       21         CIRCUT-DESIGN FORUMS.       21         STUDENT FORUM.       22         ISSCC 2009 - ANALOG.       23         OVERVIEW.       25         FEATURED PAPERS.       26         Panel       FOREWARNED IS FOUR-ARMED; CLASSIC ANALOG MISTEAKS TO AVOID.         Forum       CLOCK SYNTHESIS DESIGN         Structure Dappers.       26         Forum       CLOCK SYNTHESIS DESIGN         Special-Topic Session       INTERLEAVING ADCs - EXPLOITING THE PARALLELISM         Special-Topic Session       INTERLEAVING ADCs - EXPLOITING THE PARALLELISM     <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10000 |                      |                                                            |    |

| PLENARY SESSION       13         TECHNICAL HIGHLIGHTS       15         EVENINGA ESSIONS       19         Short Course       20         Tutorials       21         CIRCUIT-DESIGN FORUMS       21         STUDENT FORUM       22         ISSCC 2009 - ANALOG       23         OVERVIEW       25         FEATURED PAPERS       26         Panel       FOREWARNED IS FOUR-ARMED; CLASSIC ANALOG MISTEAKS TO AVOID         Forum       CLOCK SYNTHESIS DESIGN         ISSCC 2009 - DATA CONVERTERS       33         OVERVIEW       35         FEATURED PAPERS       36         Special-Topic Session       INTERLEAVING ADCs - EXPLOITING THE PARALLELISM         Syncial-Topic Session       INTERLEAVING ADCs - EXPLOITING THE PARALLELISM         Trends       41         ISSCC 2009 - HIGH PERFORMANCE DIGITAL       43         OVERVIEW       45         FORUM       46         Tutorial       MANAGING VARIATIONS THROUGH ADAPTIVE DESIGN TECHNIQUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |                      |                                                            |    |

| TECHNICAL HIGHLIGHTS       15         EVENING SESSIONS       19         Shot Course       20         Tutorials       21         CIRCUT-DESIGN FORUMS       21         STUDENT FORUM       22         ISSCC 2009 - ANALOG       23         OVERVIEW       25         FEATURED PAPERS       25         FEATURED PAPERS       25         FOREWARNED IS FOUR-ARMED; CLASSIC ANALOG MISTEAKS TO AVOID       29         Tutorial       CONTINUOUS-TIME FLITERS       30         Forum       CLOCK SYNTHESIS DESIGN       31         ISSCC 2009 - DATA CONVERTERS       33       33         OVERVIEW       35       5         FEATURED PAPERS       36       5         FORUM       CLOCK SYNTHESIS DESIGN       31         ISSCC 2009 - DATA CONVERTERS       33       36         OVERVIEW       35       5         FORUM       CLOCK SYNTHESIS DESIGN       30         Toroial       SAR ADCs       39         Forum       CLOCK SYNTHESIS DESIGN       40         Trends       41       43         OVERVIEW       45       5         FORUMED PAPERS       45       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |                      |                                                            |    |

| EVENING SESSIONS       19         Short Course       20         Tutorials       21         STUDENT FORUM       21         SSCC 2009 - ANALOG       23         OVERVIEW       25         FEATURED PAPERS       26         Panel       FOREWARNED IS FOUR-ARMED; CLASSIC ANALOG MISTEAKS TO AVOID         Forum       CLOCK SYNTHESIS DESIGN         SSCC 2009 - DATA CONVERTERS       30         FORTURED PAPERS       33         OVERVIEW       35         FEATURED PAPERS       36         Special-Topic Session       INTERLEAVING ADCs - EXPLOITING THE PARALLELISM         Strutorial       SAR ADCs         Tutorial       SAR ADCs         Special-Topic Session       30         Totorial       SAR ADCs         Ternds       41         ISSCC 2009 - HIGH PERFORMANCE DIGITAL       43         OVERVIEW       45         FEATURED PAPERS       46         Tutorial       MANAGING VARIATIONS THROUGH ADAPTIVE DESIGN TECHNIQUES         South       MUTH-DOMAIN PROCESSORS       49         Trends       50         ISSCC 2009 - IMAGERS, MEMS, MEDICAL AND DISPLAY       53         OVERVIEW       57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |                      |                                                            |    |

| Short Course       20         Tutorials       21         STUDENT FORUM       21         STUDENT FORUM       22         ISSCC 2009 – ANALOG       23         OVERVIEW       25         FEATURED PAPERS       26         Panel       FOREWARNED IS FOUR-ARMED; CLASSIC ANALOG MISTEAKS TO AVOID       29         Tutorial       CONTINUOUS-TIME FILTERS       30         FORUM       CLOCK SYNTHESIS DESIGN       31         ISSCC 2009 – DATA CONVERTERS       33       36         OVERVIEW       35       FEATURED PAPERS       36         Special-Topic Session       INTERLEAVING ADCs - EXPLOITING THE PARALLELISM       38         Storial       SAR ADCs       39       40         Trends       41       43       0VERVIEW       45         FEATURED PAPERS       46       47       48         Forum       CLOCK SYNTHESIS DESIGN TECHNIQUES       48         Forum       MULTI-DOMAIN PROCESSORS       49         Tutorial       MANAGING VARIATIONS THROUGH ADAPTIVE DESIGN TECHNIQUES       48         Forum       MULTI-DOMAIN PROCESSORS       50         Tutorial       MANAGING VARIATIONS THROUGH ADAPTIVE DESIGN TECHNIQUES       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |                      |                                                            |    |

| Tutorials       21         CIRCUIT-DESIGN FORUMS       21         STUDENT FORUM       22         ISSCC 2009 – ANALOG       23         OVERVIEW       25         FEATURED PAPERS       26         Panel       FOREWARNED IS FOUR-ARMED; CLASSIC ANALOG MISTEAKS TO AVOID.         Forum       CLOCK SYNTHESIS DESIGN         Structurial       CONTINUOUS-TIME FILTERS         OVERVIEW       35         FEATURED PAPERS.       33         OVERVIEW       35         FEATURED PAPERS.       33         OVERVIEW       35         FEATURED PAPERS.       36         Special-Topic Session       INTERLEAVING ADCS - EXPLOITING THE PARALLELISM         Manage Country       CLOCK SYNTHESIS DESIGN         Tutorial       SAR ADCS         SUBSCC 2009 - HIGH PERFORMANCE DIGITAL       43         OVERVIEW       45         FEATURED PAPERS.       46         Tutorial       MANAGING VARIATIONS THROUGH ADAPTIVE DESIGN TECHNIQUES       48         FORUM       MULT-DOMAIN PROCESSORS       50         ISSCC 2009 - IMAGERS, MEMS, MEDICAL AND DISPLAY       53         OVERVIEW       55         FEATURED PAPERS       56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |                      |                                                            |    |

| CIRCUIT-DESIGN FORUMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |                      |                                                            |    |

| STUDENT FORUM.       22         ISSCC 2009 - ANALOG       23         OVERVIEW.       25         PEATURED PAPERS.       26         Panel       FOREWARNED IS FOUR-ARMED; CLASSIC ANALOG MISTEAKS TO AVOID.         Pintorial       CONTINUOUS-TIME FLITERS         FORTUM       CLOCK SYNTHESIS DESIGN         ISSCC 2009 - DATA CONVERTERS.       33         OVERVIEW       35         FEATURED PAPERS.       33         OVERVIEW       36         Special-Topic Session       INTERLEAVING ADCs - EXPLOITING THE PARALLELISM         Tutorial       SAR ADCs         FORTUM       CLOCK SYNTHESIS DESIGN         Trends       41         ISSCC 2009 - HIGH PERFORMANCE DIGITAL       43         OVERVIEW       45         FEATURED PAPERS.       46         Tutorial       MANAGING VARIATIONS THROUGH ADAPTIVE DESIGN TECHNIQUES         AFORUM       45         FEATURED PAPERS.       50         ISSCC 2009 - IMAGEERS, MEMS, MEDICAL AND DISPLAY       53         OVERVIEW       55         FEATURED PAPERS.       57         FUTORIal       THONING BITS INTO OPTOURS.       61         Special-Topic Session       IS FABLESS MEMS FABULOUS? <td< td=""><td></td><td></td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |                      |                                                            |    |

| OVERVIEW       25         FEATURED PAPERS.       26         Panel       FOREWARNED IS FOUR-ARMED; CLASSIC ANALOG MISTEAKS TO AVOID.       29         Tutorial       CONTINUOUS-TIME FILTERS       30         Forum       CLOCK SYNTHESIS DESIGN       31         ISSCC 2009 – DATA CONVERTERS       33         OVERVIEW       35         FEATURED PAPERS.       36         Special-Topic Session       INTERLEAVING ADCs - EXPLOITING THE PARALLELISM       38         Tutorial       SAR ADCs       39         Forum       CLOCK SYNTHESIS DESIGN       40         Trends       41         ISSCC 2009 – HIGH PERFORMANCE DIGITAL       43         OVERVIEW       45         FEATURED PAPERS.       46         Tutorial       MANAGING VARIATIONS THROUGH ADAPTIVE DESIGN TECHNIQUES       48         FORUM       MULTI-DOMAIN PROCESSORS       49         Trends       50       50         ISSCC 2009 – IMAGERS, MEMS, MEDICAL AND DISPLAY       53         OVERVIEW       55       56         FEATURED PAPERS.       57         Special-Topic Session       15 FABLESS MEMS FABULOUS?       51         Special-Topic Session       15 FABLESS MEMS FABULOUS?       52<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |                      |                                                            |    |

| OVERVIEW       25         FEATURED PAPERS.       26         Panel       FOREWARNED IS FOUR-ARMED; CLASSIC ANALOG MISTEAKS TO AVOID.       29         Tutorial       CONTINUOUS-TIME FILTERS       30         Forum       CLOCK SYNTHESIS DESIGN       31         ISSCC 2009 – DATA CONVERTERS       33         OVERVIEW       35         FEATURED PAPERS.       36         Special-Topic Session       INTERLEAVING ADCs - EXPLOITING THE PARALLELISM       36         Tutorial       SAR ADCs       39         Forum       CLOCK SYNTHESIS DESIGN       40         Tutorial       SAR ADCs       41         ISSCC 2009 – HIGH PERFORMANCE DIGITAL       43         OVERVIEW       45         FEATURED PAPERS.       46         Tutorial       MANAGING VARIATIONS THROUGH ADAPTIVE DESIGN TECHNIQUES       48         Forum       MULTI-DOMAIN PROCESSORS       49         Trends       50       50         ISSCC 2009 – IMAGERS, MEMS, MEDICAL AND DISPLAY       53         OVERVIEW       55         FEATURED PAPERS.       56         Trends       50         ISSCC 2009 – IMAGERS, MEMS, MEDICAL AND DISPLAY       53         OVERVIEW       55 <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |                      |                                                            |    |

| FEATURED PAPERS.       26         Panel       FOREWARNED IS FOUR-ARMED; CLASSIC ANALOG MISTEAKS TO AVOID.       29         Tutorial       CONTINUOUS: TIME FILTERS       30         Forum       CLOCK SYNTHESIS DESIGN       31         ISSCC 2009 - DATA CONVERTERS       33         OVERVIEW       35         FEATURED PAPERS.       36         Special-Topic Session       INTERLEAVING ADCs - EXPLOITING THE PARALLELISM         Sar Tutorial       SAR ADCs         Forum       CLOCK SYNTHESIS DESIGN         Tutorial       SAR ADCs         Forum       CLOCK SYNTHESIS DESIGN         Trends       41         ISSCC 2009 - HIGH PERFORMANCE DIGITAL       43         OVERVIEW       45         FEATURED PAPERS       46         Tutorial       MANAGING VARIATIONS THROUGH ADAPTIVE DESIGN TECHNIQUES         AFORUM       49         Trends       50         ISSCC 2009 - IMAGERS, MEMS, MEDICAL AND DISPLAY       53         OVERVIEW       55         FEATURED PAPERS       57         Special-Topic Session       IS FABLESS MEMS FABULOUS?       57         Special-Topic Session       IS FABLESS MEMS FABULOUS?       53         OVERVIEW       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ISSCC | ; 2009 – ANAL(       | 0G                                                         | 23 |

| FEATURED PAPERS.       26         Panel       FOREWARNED IS FOUR-ARMED; CLASSIC ANALOG MISTEAKS TO AVOID.       29         Tutorial       CONTINUOUS: TIME FILTERS       30         Forum       CLOCK SYNTHESIS DESIGN       31         ISSCC 2009 - DATA CONVERTERS       33         OVERVIEW       35         FEATURED PAPERS.       36         Special-Topic Session       INTERLEAVING ADCs - EXPLOITING THE PARALLELISM         Sar Tutorial       SAR ADCs         Forum       CLOCK SYNTHESIS DESIGN         Tutorial       SAR ADCs         Forum       CLOCK SYNTHESIS DESIGN         Trends       41         ISSCC 2009 - HIGH PERFORMANCE DIGITAL       43         OVERVIEW       45         FEATURED PAPERS       46         Tutorial       MANAGING VARIATIONS THROUGH ADAPTIVE DESIGN TECHNIQUES         AFORUM       49         Trends       50         ISSCC 2009 - IMAGERS, MEMS, MEDICAL AND DISPLAY       53         OVERVIEW       55         FEATURED PAPERS       57         Special-Topic Session       IS FABLESS MEMS FABULOUS?       57         Special-Topic Session       IS FABLESS MEMS FABULOUS?       53         OVERVIEW       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |                      |                                                            |    |

| Tutorial       CONTINUOUS-TIME FILTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       | -                    |                                                            |    |

| Forum       CLOCK SYNTHESIS DESIGN       .31         ISSCC 2009 - DATA CONVERTERS       .33         OVERVIEW       .35         FEATURED PAPERS       .36         Special-Topic Session       INTERLEAVING ADCs - EXPLOITING THE PARALLELISM       .38         Tutorial       SAR ADCs       .39         Forum       CLOCK SYNTHESIS DESIGN       .40         Trends       .41       .41         ISSCC 2009 - HIGH PERFORMANCE DIGITAL       .43         OVERVIEW       .45         FEATURED PAPERS       .46         Tutorial       MANAGING VARIATIONS THROUGH ADAPTIVE DESIGN TECHNIQUES       .48         Forum       MULTI-DOMAIN PROCESSORS       .49         Trends       .50       .55         FEATURED PAPERS       .56       .57         Special-Topic Session       IS FABLESS MEMS FABULOUS?       .61         Special-Topic Session       INTERFACES       .62         FUTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       | Panel                | FOREWARNED IS FOUR-ARMED; CLASSIC ANALOG MISTEAKS TO AVOID | 29 |

| ISSCC 2009 - DATA CONVERTERS       33         OVERVIEW       35         FEATURED PAPERS.       36         Special-Topic Session       INTERLEAVING ADCs - EXPLOITING THE PARALLELISM       38         Tutorial       SAR ADCs       39         Forum       CLOCK SYNTHESIS DESIGN       40         Trends       41       41         ISSCC 2009 - HIGH PERFORMANCE DIGITAL       43         OVERVIEW       45         FEATURED PAPERS.       46         Tutorial       MANAGING VARIATIONS THROUGH ADAPTIVE DESIGN TECHNIQUES       48         Forum       MULTI-DOMAIN PROCESSORS       49         Trends       50       50         ISSCC 2009 - IMAGERS, MEMS, MEDICAL AND DISPLAY       53         OVERVIEW       55         FEATURED PAPERS.       51         OVERVIEW       55         FEATURED PAPERS.       51         Special-Topic Session       IS FABLESS MEMS FABULOUS?       51         Special-Topic Session       IS FABLESS MEMS FABULOUS?       61         Special-Topic Session       IS FABLESS MEMS FABULOUS?       62         Tutorial       TURNING BITS INTO PICTURES       63         Forum       MEDICAL IMAGE SENSORS       62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | Tutorial             |                                                            |    |

| OVERVIEW       35         FEATURED PAPERS.       36         Special-Topic Session       INTERLEAVING ADCs - EXPLOITING THE PARALLELISM       38         Tutorial       SAR ADCs       39         Forum       CLOCK SYNTHESIS DESIGN       40         Trends       41         ISSCC 2009 - HIGH PERFORMANCE DIGITAL       43         OVERVIEW       45         FEATURED PAPERS.       46         Tutorial       MANAGING VARIATIONS THROUGH ADAPTIVE DESIGN TECHNIQUES       48         Forum       MULTI-DOMAIN PROCESSORS       49         Trends       50       50         ISSCC 2009 - IMAGERS, MEMS, MEDICAL AND DISPLAY       53         OVERVIEW       55         FEATURED PAPERS.       57         Special-Topic Session       IS FABLESS MEMS FABULOUS?         Special-Topic Session       IS FABLESS MEMS FABULOUS?         Special-Topic Session       HGHLIGHTS OF IEDM 2008         Forum       MEDICAL IMAGE SENSORS         Forum       MEDICAL IMAGE SENSORS         Forum       MEDICAL IMAGE SENSORS         Forum       MID (TURNING BITS INTO PICTURES         Forum       INTEGRATED NEURAL INTERFACES         Trends       67         Trend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       | Forum                | CLOCK SYNTHESIS DESIGN                                     | 31 |

| OVERVIEW       35         FEATURED PAPERS.       36         Special-Topic Session       INTERLEAVING ADCs - EXPLOITING THE PARALLELISM       38         Tutorial       SAR ADCs       39         Forum       CLOCK SYNTHESIS DESIGN       40         Trends       41         ISSCC 2009 - HIGH PERFORMANCE DIGITAL       43         OVERVIEW       45         FEATURED PAPERS.       46         Tutorial       MANAGING VARIATIONS THROUGH ADAPTIVE DESIGN TECHNIQUES       48         Forum       MULTI-DOMAIN PROCESSORS       49         Trends       50       50         ISSCC 2009 - IMAGERS, MEMS, MEDICAL AND DISPLAY       53         OVERVIEW       55         FEATURED PAPERS.       57         Special-Topic Session       IS FABLESS MEMS FABULOUS?         Special-Topic Session       IS FABLESS MEMS FABULOUS?         Special-Topic Session       HGHLIGHTS OF IEDM 2008         Forum       MEDICAL IMAGE SENSORS         Forum       MEDICAL IMAGE SENSORS         Forum       MEDICAL IMAGE SENSORS         Forum       MID (TURNING BITS INTO PICTURES         Forum       INTEGRATED NEURAL INTERFACES         Trends       67         Trend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |                      |                                                            |    |

| FEATURED PAPERS.       36         Special-Topic Session       INTERLEAVING ADCs - EXPLOITING THE PARALLELISM       38         Tutorial       SAR ADCs.       39         Forum       CLOCK SYNTHESIS DESIGN       40         Trends       41         ISSCC 2009 - HIGH PERFORMANCE DIGITAL       43         OVERVIEW       45         FEATURED PAPERS.       46         Tutorial       MANAGING VARIATIONS THROUGH ADAPTIVE DESIGN TECHNIQUES       48         Forum       MULTI-DOMAIN PROCESSORS       49         Trends       50       50         ISSCC 2009 - IMAGERS, MEMS, MEDICAL AND DISPLAY       53         OVERVIEW       55         FEATURED PAPERS       57         Special-Topic Session       IS FABLESS MEMS FABULOUS?       61         Special-Topic Session       HIG FABULOUS?       61         Special-Topic Session       HIS FABULOUS?       61         Special-Topic Session       HIS FABULOUS?       61         Special-Topic Session       HIS FABULOUS?       62         Tutorial       TURNING BITS INTO PICTURES       63         Forum       INTEGRATED NEURAL INTERFACES       65         Trends       67       73         FOUERN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ISSCC | ; 2009 – DATA        | CONVERTERS                                                 | 33 |

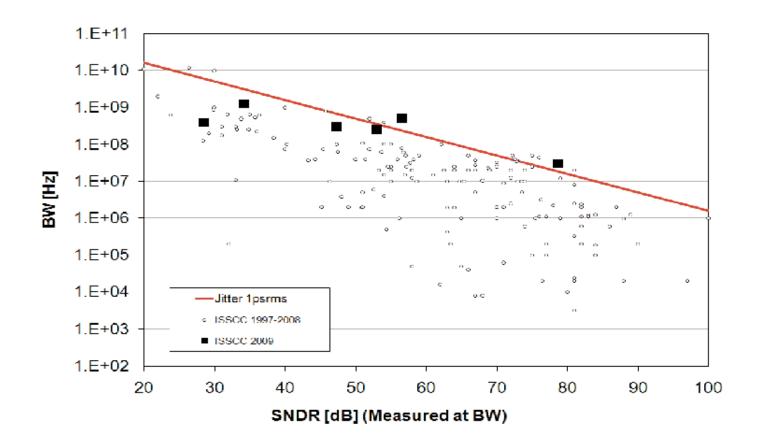

| Special-Topic Session       INTERLEAVING ADCS - EXPLOITING THE PARALLELISM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       | OVERVIEW             |                                                            | 35 |

| Tutorial       SAR ADCs       39         Forum       CLOCK SYNTHESIS DESIGN       40         Trends       41         ISSCC 2009 - HIGH PERFORMANCE DIGITAL       43         OVERVIEW       45         FEATURED PAPERS.       46         Tutorial       MANAGING VARIATIONS THROUGH ADAPTIVE DESIGN TECHNIQUES       48         Forum       MULTI-DOMAIN PROCESSORS       49         Trends       .50         ISSCC 2009 - IMAGERS, MEMS, MEDICAL AND DISPLAY       .53         OVERVIEW       .55         FEATURED PAPERS.       .57         Special-Topic Session       IS FABLESS MEMS FABULOUS?       .61         Special-Topic Session       IN FABLESS MEMS FABULOUS?       .61         Special-Topic Session       INTEGRATED NEURAL INTERFACES       .63         Forum       INETEGRATED NEURAL INTERFACES       .65         Trends       .67       .73         ISSCC 2009 - LOW-POWER DIGITAL       .71       .71         OVERVIEW       .73       .73         FORUM       .73       .74         Panel       MID - "SCALED-DOWN" PC OR "SOUPED-UP" HANDHELD?       .77         Tutorial       ADAPTIVE POWER-MANAGEMENT TECHNIQUES       .78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       | FEATURED PAPERS      |                                                            | 36 |

| Forum       CLOCK SYNTHESIS DESIGN       40         Trends       41         ISSCC 2009 - HIGH PERFORMANCE DIGITAL       43         OVERVIEW       45         FEATURED PAPERS       46         Tutorial       MANAGING VARIATIONS THROUGH ADAPTIVE DESIGN TECHNIQUES       48         Forum       MULTI-DOMAIN PROCESSORS       49         Trends       50         ISSCC 2009 - IMAGERS, MEMS, MEDICAL AND DISPLAY       53         OVERVIEW       55         FEATURED PAPERS       57         Special-Topic Session       IS FABLESS MEMS FABULOUS?       61         Special-Topic Session       HIGHLIGHTS OF IEDM 2008       62         Tutorial       TURNING BITS INTO PICTURES       63         Forum       MEDICAL IMAGE SENSORS       64         Forum       INTEGRATED NEURAL INTERFACES       65         Trends       67       67         ISSCC 2009 - LOW-POWER DIGITAL       71       73         OVERVIEW       73       73         FeatURED PAPERS       74         Panel       MID - "SCALED-DOWN" PC OR "SOUPED-UP" HANDHELD?       77         Tutorial       ADAPTIVE POWER-MARGEMENT TECHNIQUES       78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       | Special-Topic Sessio | on INTERLEAVING ADCs - EXPLOITING THE PARALLELISM          | 38 |

| Trends       41         ISSCC 2009 - HIGH PERFORMANCE DIGITAL       43         OVERVIEW       45         FEATURED PAPERS       46         Tutorial       MANAGING VARIATIONS THROUGH ADAPTIVE DESIGN TECHNIQUES       48         Forum       MULTI-DOMAIN PROCESSORS       49         Trends       50         ISSCC 2009 - IMAGERS, MEMS, MEDICAL AND DISPLAY       53         OVERVIEW       55         FEATURED PAPERS       57         Special-Topic Session       IS FABLESS MEMS FABULOUS?         Special-Topic Session       IS FABLESS MEMS FABULOUS?         Special-Topic Session       INTEGRATED NEURAL INTERFACES         Forum       MEDICAL INAGE SENSORS         Forum       MEDICAL INTERFACES         Forum       INTEGRATED NEURAL INTERFACES         OVERVIEW       73         FUTORIAL       71         OVERVIEW       73         Forum       INTEGRATED NEURAL INTERFACES         Forum       INTEGRATED NEURAL INTERFACES         Trends       67         ISSCC 2009 - LOW-POWER DIGITAL       71         OVERVIEW       73         FEATURED PAPERS       74         Panel       MID - "SCALED-DOWN" PC OR "SOUPED-UP" HANDHELD? </td <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |                      |                                                            |    |

| ISSCC 2009 – HIGH PERFORMANCE DIGITAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |                      |                                                            |    |

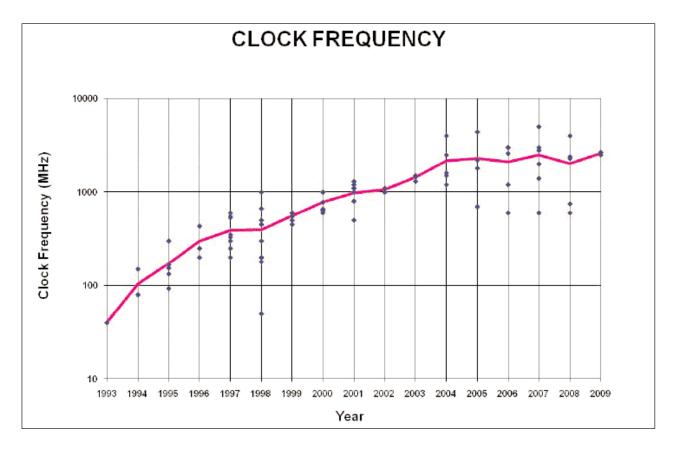

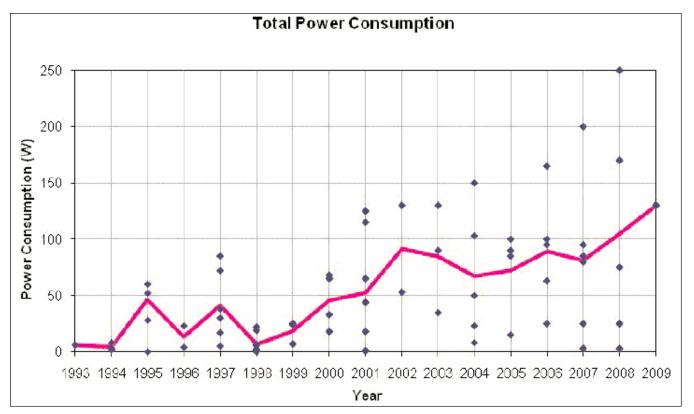

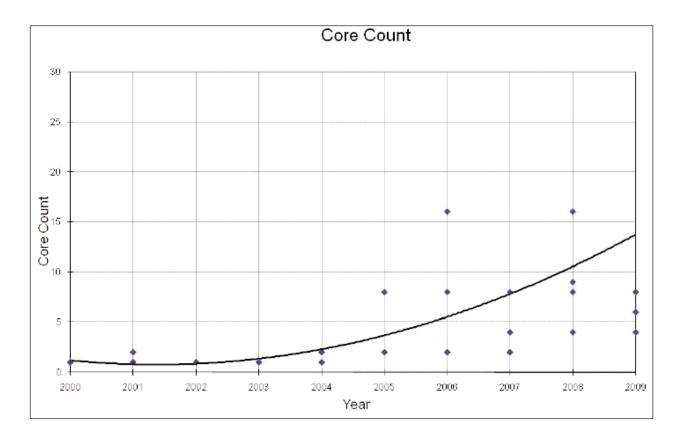

| OVERVIEW       45         FEATURED PAPERS.       46         Tutorial       MANAGING VARIATIONS THROUGH ADAPTIVE DESIGN TECHNIQUES       48         Forum       MULTI-DOMAIN PROCESSORS       49         Trends       50         ISSCC 2009 – IMAGERS, MEMS, MEDICAL AND DISPLAY         OVERVIEW       53         OVERVIEW       55         FEATURED PAPERS       57         Special-Topic Session       IS FABLESS MEMS FABULOUS?       61         Special-Topic Session       HIGHLIGHTS OF IEDM 2008       62         Tutorial       TURNING BITS INTO PICTURES       63         Forum       MEDICAL IMAGE SENSORS       64         Forum       INTEGRATED NEURAL INTERFACES       65         Trends       67       67         ISSECC 2009 – LOW-POWER DIGITAL       71       0VERVIEW         OVERVIEW       73       74         Panel       MID - "SCALED-DOWN" PC OR "SOUPED-UP" HANDHELD?       77         Tutorial       ADAPTIVE POWER-MANAGEMENT TECHNIQUES       78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | Trends               |                                                            | 41 |

| OVERVIEW       45         FEATURED PAPERS.       46         Tutorial       MANAGING VARIATIONS THROUGH ADAPTIVE DESIGN TECHNIQUES       48         Forum       MULTI-DOMAIN PROCESSORS       49         Trends       50         ISSCC 2009 – IMAGERS, MEMS, MEDICAL AND DISPLAY         OVERVIEW       55         FEATURED PAPERS.       57         Special-Topic Session       IS FABLESS MEMS FABULOUS?       61         Special-Topic Session       HIGHLIGHTS OF IEDM 2008       62         Tutorial       TURNING BITS INTO PICTURES       63         Forum       MEDICAL IMAGE SENSORS       64         Forum       INTEGRATED NEURAL INTERFACES       65         Trends       67       67         ISSCC 2009 – LOW-POWER DIGITAL       71       0VERVIEW         OVERVIEW       73       74         Panel       MID - "SCALED-DOWN" PC OR "SOUPED-UP" HANDHELD?       77         Tutorial       ADAPTIVE POWER-MANAGEMENT TECHNIQUES       78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10000 |                      |                                                            |    |

| FEATURED PAPERS       46         Tutorial       MANAGING VARIATIONS THROUGH ADAPTIVE DESIGN TECHNIQUES       48         Forum       MULTI-DOMAIN PROCESSORS       49         Trends                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19900 | , 2009 – HIGH        |                                                            | 43 |