# ADVANCE PROGRAM

# 2009 IEEE INTERNATIONAL SOLID-STATE CIRCUITS CONFERENCE

FEBRUARY 8, 9, 10, 11, 12

**CONFERENCE THEME:**

**Adaptive Circuits** and Systems

SAN FRANCISCO **MARRIOTT HOTEL**

**Replay on Demand** SEE PAGE 94

#### ISSCC VISION STATEMENT

The International Solid-State Circuits Conference is the foremost global forum for presentation of advances in solid-state circuits and systems-on-a-chip. The Conference offers a unique opportunity for engineers working at the cutting edge of IC design and application to maintain technical currency and to network with leading experts.

#### CONFERENCE HIGHLIGHTS

On Sunday, February 8th, the day before the official opening of the Conference, ISSCC 2009 offers:

- A choice of up to 4 of a total of 10 Tutorials

- Four ISSCC Advanced-Circuits-Design Forums:

- SSD: Memory Subsystem Innovation 0

- Medical Image Sensors 0

- GIRAFE : 4G RF Frontends 0

- Ultra-Low-Voltage Circuit Design

- 0 • A Student Forum featuring 5-minute presentations by selected student researchers

The 90-minute tutorials offer background information and a review of the basics in specific circuit design topics. In the all-day Advanced-Circuit-Design Forums, leading experts present state-of-the-art design strategies in a workshop-like format. The Forums are targeted at designers experienced in the technical field.

On Sunday evening, two Special-Topic Evening Sessions addressing next-generation circuit-design challenges will be offered starting at 7:30PM:

- Healthy Radios": Radio and Microwave Devices for the Health Sciences

- Is Fabless MEMS Fabulous?

The Special-Topic Evening Sessions are open to all ISSCC attendees.

On Monday, February 9th, ISSCC 2009 offers four plenary papers followed by six parallel technical sessions. A Social Hour open to all ISSCC attendees will follow the afternoon session. The Social Hour will feature posters from the winners of the joint DAC/ISSCC Student Design Contest. Monday evening features a panel discussion, "Forewarned is Four-Armed: Classic Analog Misteakes to Avoid" and three Special-Topic Evening Sessions:

- Will ADCs Overtake Binary Frontends in Backplane Signaling?

- Highlights of IEDM 2008 •

- Things All RFIC Designers Should Know (But Were Afraid to Ask)

On Tuesday, February 10th, ISSCC 2009 offers morning and afternoon technical sessions. Tuesday evening sessions include, an evening panel; "MID-"Scaled Down" PC of "Souped-Up" Handheld?" and two Special-Topic Evening Sessions

- Interleaving ADCs-Exploiting the Parallelism

- Next-Generation Energy-Scavenging System •

Wednesday, February 11th features morning and afternoon technical sessions.

On Thursday, February 12th, ISSCC 2009 offers a choice of five events:

- An ISSCC Short Course: "Low-Voltage Analog and Mixed-Signal CMOS Circuit Design". Two sessions of the Short Course will be offered, with staggered starting times.

- Four ISSCC Advanced-Circuits-Design Forums:

- ATAC: High-Speed Interfaces  $\cap$

- Multi-Domain Processors 0

- **Clock Synthesis Design** 0

- Integrated Neural Interfaces 0

Registration for educational events will be filled on a first-come, first-served basis. Use of the ISSCC web-registration site (www.isscc.org) is strongly encouraged. You will be provided with immediate confirmation on registration for Tutorials, Advanced-Circuit-Design Forums and the Short Course.

This year, attendees will be able to register for unlimited on-demand web access to multi-media replay of ISSCC technical papers. Attendees will be able to listen to papers they could not attend or to re-play a paper they attended for better understanding.

## **CONFERENCE INFORMATION**

| Tutorials |                                                                                                                              |       |

|-----------|------------------------------------------------------------------------------------------------------------------------------|-------|

|           | FORUMS                                                                                                                       |       |

| F1        | SSD, Memory Subsystem Innovation                                                                                             |       |

| F2        | Medical Image Sensors                                                                                                        |       |

| F3        | GIRAFE: 4G RF Frontends                                                                                                      |       |

| F4        | Ultra-Low-Voltage Circuit Design                                                                                             |       |

|           | EVENING SESSIONS                                                                                                             |       |

| SE1       | "Healthy Radios": Radio/Microwave Devices for the Health Sciences                                                            |       |

| SE2       | Is Fabless MEMs Fabulous?                                                                                                    |       |

|           | PAPER SESSIONS                                                                                                               |       |

| 1         | Plenary Session                                                                                                              | 15-17 |

| 2         | Imagers                                                                                                                      |       |

| 2<br>3    |                                                                                                                              |       |

| 3<br>4    | Microprocessor Technologies<br>High-Speed Data Converters                                                                    |       |

|           |                                                                                                                              |       |

| 5<br>6    | Potpourri: PLL, Optical, DSL<br>Cellular and Tuner                                                                           |       |

| 0         |                                                                                                                              |       |

| 050       | EVENING SESSIONS                                                                                                             | 00    |

| SE3       | Will ADCs Overtake Binary Frontends in Backplane Signaling?                                                                  |       |

| SE4       | Highlights of IEDM2008                                                                                                       |       |

| E1<br>SE5 | Forewarned is Four-Armed: Classic Analog Misteakes to Avoid<br>Things all RFIC Designers Should Know (But are Afraid to Ask) |       |

| 9E0       | Things all KFIG Designers Should Khow (but are Allald to Ask)                                                                |       |

| _         | PAPER SESSIONS                                                                                                               |       |

| 7         | DRAM                                                                                                                         |       |

| 8         | Multimedia Processors                                                                                                        |       |

| 9         | Data Converter Techniques                                                                                                    |       |

| 10        | Multi-Gb/s Serial Links and Building Blocks                                                                                  |       |

| 11        | TD: Trends in Wireless Communications                                                                                        |       |

| 12        | RF Building Blocks                                                                                                           |       |

| 13        | Flash Memory                                                                                                                 |       |

| 14        | Digital Wireless and Reconfigurability                                                                                       |       |

| 15        | Display and Imager Electronics                                                                                               |       |

| 16        | High-Speed and mm-Wave Circuits                                                                                              |       |

| 17        | TD: Energy-Aware Sensor Systems                                                                                              |       |

|           | rence Timetable                                                                                                              |       |

| 18        | Ranging and Gb/s Communication                                                                                               |       |

| 19        | Analog Techniques                                                                                                            | 56-57 |

|           | EVENING SESSIONS                                                                                                             |       |

| SE6       | Interleaving ADC's – Exploiting the Parallelism                                                                              |       |

| SE7       | Next-Generation-Energy Scavenging System                                                                                     |       |

| E2        | MID – "Scaled Down" PC or "Souped Up" Handheld?                                                                              | 59    |

|           | PAPER SESSIONS                                                                                                               |       |

| 20        | Sensors and MEMS                                                                                                             | 60-61 |

| 21        | 10Gb/s-to-40Gb/s Transmitters and Receivers                                                                                  |       |

| 22        | PA and Antenna Interface                                                                                                     |       |

| 23        | PLLs and Clocks                                                                                                              |       |

| 24        | Wireless Connectivity                                                                                                        |       |

| 25        | Medical                                                                                                                      |       |

| 26        | Switched-Mode Techniques                                                                                                     |       |

| 27        | SRAM and Emerging Memory                                                                                                     |       |

| 28        | TD: Directions in Computing and Signaling                                                                                    |       |

| 20<br>29  | mm-Wave Circuits                                                                                                             |       |

| 23        | mm-wave oncults                                                                                                              |       |

|           | SHORT COURSE                                                                                                                 |       |

| Low-V     | Oltage Analog and Mixed-Signal CMOS Circuit Design                                                                           | 80-82 |

|           |                                                                                                                              |       |

#### FORUMS

| F5                     | ATAC: High-Speed Interfaces  |  |

|------------------------|------------------------------|--|

| F6                     | Multi-Domain Processors      |  |

|                        | Clock Synthesis Design       |  |

| F8                     | Integrated Neural Interfaces |  |

| Information            |                              |  |

| Committees             |                              |  |

| Conference Information |                              |  |

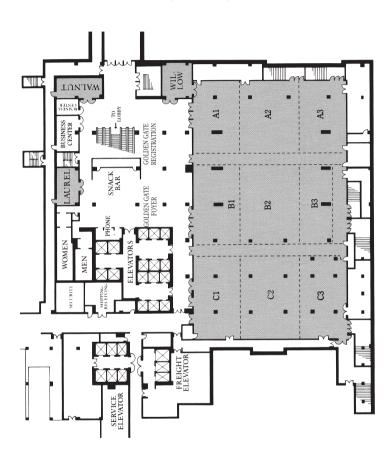

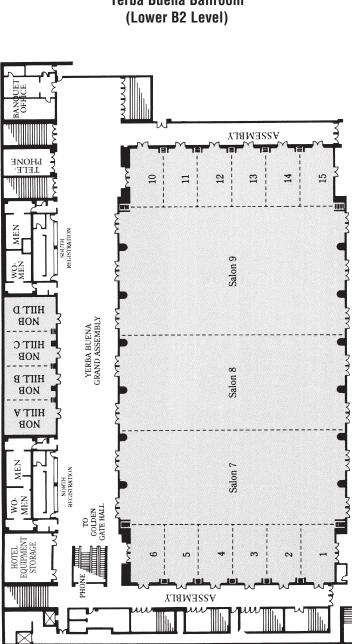

| Hotel Layout           |                              |  |

|                        |                              |  |

**Celebrating 125 Years**

of Engineering the Future

#### Celebrate IEEE's 125th Anniversary

Tracing its roots to the formation of the American Institute of Electrical Engineers in 1884 by such pioneers as Thomas Alva Edison and Alexander Graham Bell, today's global IEEE is celebrating its 125<sup>th</sup> anniversary in 2009. Join with us as we commemorate 125 years of ingenuity and innovation in engineering and technology with activities that support the anniversary theme, "Celebrating 125 Years of Engineering the Future."

The year-long IEEE celebration honors the past and focuses on the future with special events at major conferences such as ISSCC. Other anniversary activities around the world include: member and customer events in major world cities; the first student World Congress; the Inaugural IEEE Presidents' "Change the World Competition" for university students; a media roundtable and global webcast featuring emerging, world-changing technologies; IEEE "Engineering the Future Day", on 13 May 2009, the official anniversary date; an IEEE History Center conference and gala; and much more.

All ISSCC attendees are encouraged to take an active role during this milestone anniversary to honor the countless contributions our members and the technology professions have made that have helped change the world. Celebrate with IEEE as we champion the development of future technologies that will benefit humanity.

For more information on the IEEE 125th Anniversary, or to participate online, visit http://www.ieee125.org.

#### T1: Continuous-Time Filters

Filters are used everywhere in integrated systems. While it is true that precision filtering at low-to-moderate frequencies is best done in the digital domain, the need for continuous-time analog filters has not gone away. Anti-aliasing and reconstruction is always present even for moderate frequency signals, and at high frequencies, analog filters still offer advantages in power. With pressure on the curriculum in all universities, there is less coverage of filter techniques in EE courses, and engineers must pick up the tools on the job. This tutorial aims to lay out the groundwork theory and illustrate the mainstream strategies for integrated continuous-time filters. Topics to be covered include:

- Filter applications and system demands

- Filter specifications and approximations

- Filter realizations and topologies: single-amplifier, biquad, leapfrog

- Integrated implementations: opamp-RC, gm-C

- Tuning strategies: variable elements, digital tuning

**Instructor: Bill Redman-White** is currently a fellow with NXP Semiconductors UK. He has also worked in France and California on optical storage, cellular radio, WLAN, digital audio, TV, and satellite baseband. He was previously with Motorola Geneva, GEC Marconi, and British Telecom, UK. Concurrently with NXP, he is also a Professor at Southampton University undertaking teaching and research in analog, RF, and SOI CMOS.

#### T2: Adaptive Power Management Techniques

As highlighted by the conference theme of Adaptive Circuits and Systems, increasingly adaptive techniques are used to manage power dissipation of SoCs. These SoCs are integrating more transistors per die, facing worsening leakage dissipation with each process node and are operating at ever-higher processor frequencies. State-of-the-art adaptive power management techniques such as adaptive voltage scaling, body bias, power gating, dynamic voltage-frequency scaling and sleep modes are discussed both in theory and through examples of implementations found in practice.

**Instructor: Alice Wang** is currently Senior Member of Technical Staff at Texas Instruments in Dallas, Texas. She is involved in the design of SoCs in the Wireless Terminal Business Unit for application in digital baseband and application processors in cellular phones, focusing on low-power techniques and enhancing battery lifetimes. She received her PhD from the Electrical Engineering department at Massachusetts Institute of Technology, in 2004. Part of her PhD thesis work demonstrated the first-ever 180mV sub-threshold FFT processor.

#### T3: Turning Bits into Pictures

Electronic displays are deployed in a variety of applications, each of which priorities particular performance criteria (e.g., image quality, size, definition and brightness) whilst imposing its own constraints (e.g., cost, power consumption, robustness). The performance criteria must be met by innovations in electro-optic technology (e.g. LCD, OLED), electronic technology (e.g. LTPS, a-Si) and electronic design. Attendees should leave this tutorial with an understanding of the electronic architectures and circuits that contribute to meeting user expectations in modern display systems.

**Instructor: Ian Underwood** carried out pioneering R&D in LC microdisplays between 1983 and 1999 when he co-founded MicroEmissive Displays Ltd (MED) as co-inventor of its P-OLED microdisplay technology.. He was a Fulbright Fellow (1991) at the University of Colorado, Photonics Spectra Circle of Excellence designer (1994), British Telecom Fellow (1997), Ben Sturgeon Award winner (1999), Ernst & Young Emerging Entrepreneur of the Year (2003), Fellow of the Royal Society of Edinburgh (2004), Gannochy Medal winner (2004), Fellow of the Institute of Physics (2008) and Fellow of the Royal Academy of Engineering (2008). He is a Professor of Electronic Displays at the University of Edinburgh, Associate Editor of JSID, and a member of the program committees of ISSCC 2009, SID Displays Week 2009 and Eurodisplay/IDRC 2009. He is co-author of the book Introduction to Microdisplays (2006) and is recognized worldwide as an authority on microdisplay technology, systems and applications.

#### T4: Fundamentals of Digitally-Assisted RF

RF circuits, when implemented in nanoscale CMOS and, especially, when integrated in an SoC, suffer from numerous issues, such as poor linearity, device mismatch, low  $V_{dd}$  headroom, high leakage, high flicker and substrate noise, etc. At the same time, the digital gates and memory are 'free' and powerful, so the logical step is to use digital means to mitigate the RF circuit imperfections so that their adjusted performance can match or exceed that of traditional RF circuits. This tutorial first examines opportunities for digital assistance of RF and then presents case studies of calibration due to process spread, compensation due to environmental changes, performance tuning, automatic reconfigurability, and built-in self-test.

**Instructor: Robert Bogdan Staszewski** received his PhD from the University of Texas at Dallas in 2002 for his research on RF frequency synthesis in digital deep-submicron CMOS. From 1991 to 1995, he worked at Alcatel Network Systems in Richardson, TX. He joined Texas Instruments in Dallas, TX, in 1995 where he holds an elected title of Distinguished Member of Technical Staff for his pioneering work on Digital RF Processor (DRP<sup>TM</sup>) architecture. He is currently a Chief Technical Officer (CTO) of the DRP system and design development group. He has authored and co-authored 80 journal and conference publications and holds 40 issued and 60 pending US patents.

#### T5: Display and RFID-Tag Design Using Organic Transistors

Electronics based on organic semiconductors has demonstrated its potential to enable printing of complex electronics functions on large-area, paper-like, flexible surfaces. Using high-speed throughput printing instead of the conventional lithography-based manufacturing technology should also enable low-cost products. Typical organic electronics applications are flexible displays, solar cells, light-emitting surfaces, RFIDs and physical, chemical or bio sensors.

This tutorial presents basic modeling of thin-film transistors manufactured with organic semiconductors (OTFTs) and state-of-the-art techniques to design, using organic TFTs, display backplanes, digital electronics and RFID radios.

**Instructor: E. Cantatore** received his PhD in Electrical Engineering from Politecnico di Bari, Italy in 1998. After a postdoc at CERN, Geneva, Switzerland, where he worked on radiation-hard electronics for particle sensors, he joined Philips Research, Eindhoven, The Netherlands. At Philips he designed some of the first displays based on organic transistor backplanes and strongly contributed to the development of organic RFIDs. His research interests cover as well ultra-low-power analog CMOS design and biomedical applications. In 2007, he joined the Electrical Engineering department of the Eindhoven University of Technology. He has published more than 70 papers in international conferences and journals, holds 10 patents and patent applications and gave invited talks on organic electronics at ESSDERC, DATE, ESSCIRC, BCTM and E-MRS. He serves on the ITPC of ESSDERC and ISSCC, which granted him, in 2006, the Beatrice Winner Award for a paper on organic RFIDs.

#### T6: SAR ADCs

Technology scaling is offering MOS transistors with higher-frequency capabilities but lower inherent analog gain.

In this scenario, ADC designers must account for the performance sensitivity of their converters to decreasing opamp gain. Thus, alternative ADC topologies that can trade higher operation speed with lower opamp-gain sensitivity have to be developed. Successive-approximation register (SAR) structures are one of the candidate topologies that have experienced a resurgence in recent years.

In this tutorial the basic concepts underlying SAR ADCs will be presented. The most popular implementations will be discussed (charge redistribution, resistive DACs, charge sharing), and recent developments that have allowed SAR ADCs to become the record holders in terms of ADC figure-of-merit will be introduced (redundancy, comparator noise tolerance).

**Instructor:** Andrea Baschirotto is an Associate Professor at the University of Milano-Bicocca. His main research interests are in the design of mixed-analog/digital integrated circuits, in particular for low-power and/or high-speed signal processing. He has authored or co-authored more than 190 papers in international journals and presentations at international conferences, 1 book, 6 book chapters, and holds 29 USA patents. He has been Associate Editor for the IEEE Transactions on Circuits Systems: Parts I and II. He was the Technical Program Committee Chairman for ESSCIRC 2002. He has collaborated with several companies on the design of mixed-signal ASICs. He participates in several research collaborations, also funded by national and European projects.

#### T7: Managing Variations Through Adaptive Design Techniques

CMOS technology scaling has given rise to increased sensitivity of design to process, voltage and temperature (PVT) variations as well as to aging effects. These uncertainties have led to ever-larger design margins intended to ensure correct operation under all conditions which result in substantial performance and power losses. In this context, a new trend in adaptive design techniques has emerged where circuits are dynamically adjusted at runtime to compensate for PVT and aging effects. This Tutorial reviews the sources of uncertainty and their classification, and describes techniques for dynamic compensation and adaptive control. Particular emphasis is given to so-called canary circuits, PVT monitors, and adaptive voltage and frequency synthesis. The discussion examines current industrial practice as well as highlighting future trends coming from industrial and academic research.

**Instructor: David Blaauw** received his BS in Computer Science and Physics from Duke University and his Ph.D. in Computer Science from the University of Illinois, Urbana-Champaign. He worked for Motorola for 8 years as a manager in the Advanced Design Technology group. Since 2001, he has been on the faculty at the University of Michigan, Ann Arbor. His research interests include low-power and high-performance design. He has authored over 250 papers and holds 25 patents. He is a member of the ISSCC Technical Program Committee and has served as chair of the International Symposium on Low Power Electronic Design (ISLPED) and as an executive committee member of the Design Automation Conference.

#### T8: Variation-Tolerant SRAM Circuit Designs

This Tutorial begins with a discussion of a basic understanding of SRAMs and then describes the challenges and some of the key circuits required for a robust design. Threshold-voltage variation is a critical factor in designing memories at 45nm and below, due to process variation. Various circuit techniques that enable continued area and voltage scaling are shared in this Tutorial. Comparison of the circuit techniques presented at leading conferences for design of 65nm and beyond are discussed, and an overview is presented.

Statistical design methods along with circuit-based design-margin assist techniques and their effect on process, voltage, and temperature variations are discussed in detail.

- Overview of SRAM applications and scaling

- Operating voltage and area scaling trends and key challenges

- Static-noise margin (SNM)

- Write margin (WŘM)

- Cell-current margin (ICELL)

- Statistical-margin analysis methods

- Circuit-design techniques

- Discussion of the scalability of circuit techniques

**Instructor: Hiroyuki Yamauchi** is a Professor at the Fukuoka Institute of Technology in Fukuoka, Japan. Previously, he worked for Panasonic in Japan for 20 years, having responsibility as a general manager for developing embedded SRAM, DRAM, and nonvolatile memories. He has invented and developed various SRAM and DRAM circuit design techniques, such as charge-recycling data-bus architecture and a control scheme for elevating SRAM source line potential for leakage reduction and variability tolerance. He holds 87 US patents and has published over 40 papers in the area of memory design. He received his PhD in Engineering in 1997 from the University of Kyushu in Fukuoka, Japan.

#### **T9: Managing Linearity in Radio Front-Ends**

Radio front-end linearity requirements can pose a major challenge in the design of receivers for several commercial wireless systems. In this presentation, we will explore circuit techniques and architectures that address this issue, with an emphasis on approaches that reduce the requirement for off-chip passive filters. Basic concepts related to front-end dynamic range, including noise performance and mechanisms for non-linearity-induced performance degradation will be introduced. Design approaches that are useful for improving receiver linearity, such as feedback and feedforward; the use of on-chip filters and frequency-selective terminations; and approaches that utilize multiple receiver paths will be presented, along with relevant examples from practical wireless systems. The impact of these techniques on dynamic range will be considered.

**Instructor: Ranjit Gharpurey** is an Associate Professor in the Department of Electrical and Computer Engineering at the University of Texas at Austin. His primary research interests are in the areas of high-frequency and high-speed circuit design with emphasis on RFIC design for wireless applications, and parasitic noise sources in integrated circuits. He received his Ph. D. from the University of California at Berkeley in 1995 and his B. Tech (Bachelor of Technology) from the Indian Institute of Technology, Kharagpur, India in 1990.

#### T10: CMOS Circuit Techniques for High-Speed Wireline Transceivers

This tutorial covers the modern CMOS design techniques for high-speed wireline communications operating at tens of Gb/s. Starting from the architecture-level illustration which explains the necessity and applications of the high-speed blocks, this talk conveys popular design skills and typical considerations on voltage-controlled oscillators, frequency dividers, and broadband amplifiers. Design methodology will be included to investigate the circuit optimization, and case study will be given in the end to introduce the state-of-the-art.

**Instructor:** Jri Lee received the M.S. and Ph.D. degrees in electrical engineering from the University of California, Los Angeles (UCLA), both in 2003. He joined National Taiwan University (NTU) since 2004, where he is currently Associate Professor of electrical engineering. He is now serving in the Technical Program Committees of the ISSCC, Symposium on VLSI Circuits, and A-SSCC. Prof. Lee received the Beatrice Winner Award for Editorial Excellence at the 2007 ISSCC, the Takuo Sugano Award for Outstanding Far-East Paper at the 2008 ISSCC, and NTU Outstanding Teaching Award in 2007 and 2008.

#### F1: SSD Memory Subsystem Innovation

| Organizer & Session Chair: | Ken Takeuchi, University of Tokyo, Tokyo, Japan    |

|----------------------------|----------------------------------------------------|

| Organizing Committee:      | Hideto Hidaka, Renesas Technology, Itami, Japan    |

|                            | Frankie Roohparvar, Micron, San Jose, CA           |

|                            | Kevin Zhang, Intel, Hillsboro, OR                  |

|                            | Mark Bauer, Numonyx, Folsom, CA                    |

|                            | Roberto Gastaldi, Numonyx, Brianza, Italy          |

|                            | Joo Sun Choi, Samsung Electronics, Gyeonggi, Korea |

|                            | Dae Seok Byeon, Samsung Electronics, Gyeonggi,     |

|                            | Korea                                              |

|                            | Daisaburo Takashima, Toshiba, Yokohama, Japan      |

This Forum addresses a broad range of key technical challenges facing designers of today's VLSI memory systems. The Forum starts with an overview of microprocessor memory architectures. It explores the challenges, implications and options available to remove traditional memory bottlenecks such as memory latency, memory bandwidth, and off-package bandwidth in the Moore's-Law-driven multi- and many-core systems. Next, system-level memory architecture is addressed. The widespread use of NAND Flash memories in SSDs and caches has opened new avenues of innovation for the enterprise- and client-computing segments. System-wide architectural changes are required to make full use of the advantages of SSDs in terms of performance, reliability and power. Circuit design and reliability challenges of NAND-Flash-memory-based SSDs are also discussed. In emerging multimedia applications, a higher bandwidth and therefore a faster-random-access memory is required. NAND flash memory is also playing a more important role because write-performance improvement improves user experience of high-speed wireless downloads. This Forum also discusses fusion memory where innovative memory designs provide flexibility to handset manufacturers allowing them to better balance cost and performance of many types of multimedia handset designs. In addition, in the Forum, three key emerging nonvolatile memories (PCRAM, FeRAM, and MRAM) and their memory systems are examined. Nonvolatile random-access memory is becoming a viable alternative to commonly used volatile and nonvolatile memories in the marketplace. Being bit-alterable like DRAM, nonvolatile like Flash, and CMOS-process compatible, nonvolatile random-access memory has the potential to revolutionize many aspects of computing-platform architectures. Further, the Forum also discusses leading-edge emerging memories and their application to computing and storage architectures. The Forum also provides an excellent opportunity for the attendees to interactively engage with the speakers on any key technical issues they may face in their product development.

## Forum Agenda

| <u>Time</u> | <u>Topics</u>                                                                |

|-------------|------------------------------------------------------------------------------|

| 8:00        | Breakfast                                                                    |

| 8:20        | Introduction<br>Ken Takeuchi, University of Tokyo, Tokyo, Japan              |

| 8:30        | Microprocessor Memory Architecture<br>Konrad Lai, Intel, Hillsboro, OR       |

| 9:20        | System-level Memory Architecture<br>Amber Huffman, Intel, Hillsboro, OR      |

| 10:10       | Break                                                                        |

| 10:25       | NAND Flash Memory Circuit<br>Daisaburo Takashima, Toshiba, Yokohama, Japan   |

| 11:15       | NAND Flash Memory Reliability<br>Seiichi Aritome, Powerchip, Hsinchu, Taiwan |

| 12:05       | Lunch                                                                        |

| 1:00        | SSD<br>Dean Klein, Micron, Boise, Boise, ID                                  |

| 1:50        | Fusion Memory and Memory System,<br>Tony Kim, Samsung, San Jose, CA          |

| 2:40        | Break                                                                        |

| 2:55        | PCRAM and Memory System,<br>Sean Eilert, Numonyx, Santa Clara, CA            |

| 3:45        | FeRAM and Memory System,<br>Hiromitsu Kimura, Rohm, Kyoto, Japan             |

| 4:35        | MRAM and Memory System,<br>Tadahiko Sugibayashi, NEC, Sagamihara, Japan      |

| 5:25        | Conclusion                                                                   |

#### F2: Medical Image Sensors

| Organizer: | Boyd Fowler, Fairchild Imaging, Milpitas, CA        |

|------------|-----------------------------------------------------|

| Committee: | Makoto Ikeda, University of Tokyo, Tokyo, Japan     |

|            | Hirofumi Sumi, Sony, Kanagawa, Japan                |

|            | Jan Bosiers, Dalsa Professional Imaging, Eindhoven, |

|            | Netherlands                                         |

|            | Johannes Solhusvik, Aptina Imaging, Oslo, Norway    |

|            | Daniel McGrath, Eastman Kodak, Rochester, NY        |

Although image sensors in medical and biotech applications are ubiquitous, new technologies and applications are being developed every year. CCD, CMOS, and TFT image sensor technologies are fueling these applications and enabling lower-cost and higher-performance systems. This forum is focused on presenting the newest image-sensor technologies and applications for the medical and biotech markets. The speakers at this forum are experts in their fields. They are invited to present the latest material on the various topics. The goal of this forum is to give engineers and their management an in-depth view of these technologies and their future directions.

#### Forum Agenda:

| <u>Time</u> | Topic                                                                                                           |

|-------------|-----------------------------------------------------------------------------------------------------------------|

| 8:00        | Breakfast                                                                                                       |

| 8:15        | Introduction<br>Boyd Fowler, Fairchild Imaging, CA                                                              |

| 8:30        | Medical Image Sensor Technology Overview<br>Keishi Kitamura, Shimadzu Medical Systems Division,<br>Kyoto, Japan |

| 9:30        | Dental Radiography<br>Chiao Liu, Fairchild Imaging, Milpitas, CA                                                |

| 10:30       | Break                                                                                                           |

| 11:00       | Medical Radiography<br>Tim Tredwell, Carestream Health, Rochester, NY                                           |

| 12:00       | Lunch                                                                                                           |

| 1:00        | Endoscopy<br>Jeffrey Adair, Micro-Imaging Solutions, San Clemente, CA                                           |

| 2:00        | Luminescence and Fluorescence Imaging<br>Mark Schnitzer, Stanford University, Stanford, CA                      |

| 3:00        | Break                                                                                                           |

| 3:30        | Retinal Implants<br>Jun Ohta, Nara Institute of Science & Technology, Nara, Japar                               |

| 4:30        | Panel Discussion and Conclusions                                                                                |

#### F3: GIRAFE: 4G RF Frontends

| Organizer:    | Stefan Heinen, RWTH Aachen University, Aachen, Germany                                                                                                                                                                                                                                                        |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Co-Organizer: | Domine Leenaerts, NXP, Eindhoven, Netherlands                                                                                                                                                                                                                                                                 |

| Committee:    | Tony Montalvo, Analog Devices, Raleigh, NC<br>Satoshi Tanaka, Renesas, Komoro, Japan<br>Domine Leenaerts, NXP, Eindhoven, Netherlands<br>Aarno Pärssinen, Nokia Corporation, Helsinki, Finland<br>Didier Belot, ST Microelectronics, Crolles, France<br>Marc Tiebout, Infineon Technologies, Villach, Austria |

Digital cellular standards have emerged over the last 20 years. Today, 2G systems like GSM/EDGE are providing worldwide coverage for voice and basic data services. The increasing demand of true mobile users for high-speed data services has forced the development of 3G toward HSPA. The next step in this evolution is the adoption of OFDM for cellular applications in systems like WiMAX and LTE. The user equipment should be compatible with all standards from 2G up to 4G in order to provide the best possible experience to the end user.

Therefore, the integration of RF transceivers must cope with multiple frequency bands, and multiple modulation schemes as well as MIMO techniques. Nanoscale CMOS provides the flexibility to integrate reconfigurable circuits, which are enhanced or assisted by elaborate digital techniques like calibration, predistortion and  $\Delta\Sigma$  modulation.

Moreover, the speed of nanoscale CMOS will open the opportunity for new "Digital RF" techniques.

Last but not least the RF transceiver must address the issue of an increasing number of frequency bands in order to keep the form factor of the phone constant. The elimination of bulky front-end filters and the reduction of the number of required power amplifiers will be a future challenge.

The forum will conclude with a panel discussion addressing the question "4G Introduction: Revolution or Evolution?" where the attendees have the opportunity to ask questions and to share their views.

Attendance is limited and pre-registration is required. This all-day forum encourages open information exchange.

The targeted participants are circuit designers and concept engineers working on wireless systems, who want to learn about the impact of nanoscale technologies in circuit and system design.

## Forum Agenda

| <u>Time</u> | <u>Topic</u>                                                                                      |

|-------------|---------------------------------------------------------------------------------------------------|

| 8:00        | Breakfast                                                                                         |

| 8:15        | Introduction<br>Stefan Heinen, RWTH Aachen University, Aachen, Germany                            |

| 8:30        | Next Generation Mobile Access Network –Super 3G and beyond–<br>Atsushi Murase, NTT DOCOMO, Japan  |

| 9:15        | RF Challenges for 3G, 4G and Beyond.<br>Stefan Heinen, RWTH Aachen University, Aachen, Germany    |

| 10:00       | Break                                                                                             |

| 10:30       | Wireless Communications ICs: Trends for 3G and LTE<br>Sven Mattisson, Ericsson, Lund, Sweden      |

| 11:15       | RF Transceivers from 3.x Toward 4G/OFDM-Based Systems<br>Christopher Hull, Intel, Hillsboro, OR   |

| 12:00       | Lunch                                                                                             |

| 1:00        | Reconfigurable RF Front-Ends for 3.9G and 4G<br>Pasi Tikka, EPCOS, Munich, Germany                |

| 1:45        | Reconfigurable ADCs for 3.xG and 4G<br>Yiannos Manoli, IMTEK, Freiburg, Germany                   |

| 2:30        | Break                                                                                             |

| 3:15        | SDR RF Front-Ends<br>Asad Abidi, University of California, Los Angeles, CA                        |

| 4:00        | Application of SDR Softransceivers to 4G Markets<br>Geoff Dawe, BitWave Semiconductor, Lowell, MA |

| 4:45        | Panel Discussion                                                                                  |

| 5:15        | Conclusion                                                                                        |

#### F4: Ultra-Low-Voltage Circuit Design

| Organizer: | Rajeevan Amirtharajah, University of California, Davis, CA |

|------------|------------------------------------------------------------|

| Committee: | Tzi-Dar Chiueh, National Taiwan University, Taipei, Taiwan |

|            | Ram Krishnamurthy, Intel, Hillsboro, OR                    |

|            | Jos Huisken, IMEC, Eindhoven, Netherlands                  |

|            | Siva Narendra, Tyfone, Portland, OR                        |

|            | Steffen Paul, Universität Bremen, Bremen, Germany          |

|            | Pascal Urard, STMicroelectronics, Crolles, France          |

|            | Alice Wang, Texas Instruments, Dallas, TX                  |

Low-power CMOS design has relied heavily on V<sub>DD</sub> scaling, in the past, to exploit the quadratic dependence of dynamic power and the exponential dependence of leakage power on voltage. Today, leading-edge low-voltage designs are pushing FET operation into the weak inversion and subthreshold regimes. Investigators around the world are reporting circuits at voltages between 180mV and 700mV that offer performance that could support a range of applications in wireless sensors, mobile phones, biomedical devices, and ultra-mobile PC's. However, these circuits are highly sensitive to variations in temperature and process. Ultra-low-voltage circuits will be increasingly challenging to design as feature sizes shrink. Current trends indicate nominal supply voltages are unlikely to be reduced much below 1V, transistor threshold voltages will likely remain between 0.3 and 0.4V to manage subthreshold leakage, and effects such as random dopant fluctuation will increase the spread in transistor parameters, all of which create difficulties in designing robust circuits at low VDD. This forum brings together leading experts to describe future challenges in ultra-low-voltage design, to explore ultra-lowvoltage circuit techniques, and to stimulate thinking about prospects for future ultralow-voltage high-volume products.

### Forum Agenda

.

| <u>11me</u><br>8:00 | <u>10pic</u><br>Breakfast                                                                                              |

|---------------------|------------------------------------------------------------------------------------------------------------------------|

| 8:20                | Introduction                                                                                                           |

| 0.20                | Raj Amirtharajah, University of California, Davis, CA                                                                  |

| 8:30                | Motivation for Ultra-low Voltage / Low Power Designs<br>Christian Piguet, CSEM, Neuchatel, Switzerland                 |

| 9:10                | Technology Scaling and Challenges for Ultra-low Voltage Design<br>Kaushik Roy, Purdue University, West Lafayette, IN   |

| 9:50                | Break                                                                                                                  |

| 10:10               | Device Sizing for Variability in Energy Constrained Systems<br>Dennis Sylvester, University of Michigan, Ann Arbor, MI |

| 10:50               | Variability and Ultra-low Voltage Logic Design<br>Takayasu Sakurai, University of Tokyo, Tokyo, Japan                  |

| 11:30               | Ultra-low Voltage Microprocessor Design: Challenges and Solutions<br>Ram Krishnamurthy, Intel, Hillsboro, OR           |

| 12:10               | Lunch                                                                                                                  |

| 1:00                | Challenges and Opportunities for Scaled Low Voltage SRAM<br>Ben Calhoun, University of Virginia, Charlottesville, VA   |

| 1:40                | Ultra-low Voltage Analog Circuit Design<br>Christian Enz, EPFL, Lausanne, Switzerland                                  |

| 2:20                | Probabilistic CMOS (PCMOS) Logic for Nanoscale Circuit Design<br>Krishna Palem, Rice University, Houston, TX           |

| 3:00                | Break                                                                                                                  |

| 3:20                | Panel Discussion: Future Prospects for Ultra-low Voltage Design in<br>Commercial Products                              |

| 4:10                | Conclusion                                                                                                             |

#### SE1: Healthy Radios: Radio & Microwave Devices for the Health Sciences

#### Organizer: Jacques C. Rudell, University of Washington, Seattle, WA Ali Hajimiri, Caltech, Pasadena, CA

#### Chair:

#### Jacques C. Rudell, University of Washington, Seattle, WA

More than a century ago, Guglielmo Marconi made the first transatlantic radio transmission which forever changed the way people exchange information with one another. Scientists and engineers have spent the better part of the last century developing more efficient radio circuits, systems and software for wireless communication. Recently, the scientific community has begun exploring the use of radio-frequency circuits for biomedical applications. These "Healthy Radios" can be categorized into two sub-topics. The first is the use of radios to communicate sensed information from the human body to the outside world. The second is the use of traditional radio circuits for medical analysis. The first two speakers in the "Healthy Radio" session explore the use of radio circuits for biomedical sensing and diagnosis, such as early cancer detection or Protein and DNA analysis. The next two speakers (BAN) and implantable devices. The session concludes with an overview of the state-of-the-art in CMOS medical imaging.

- <u>Time</u><u>Topic</u>

- 8:00 CMOS RF Biosensor Utilizing Nuclear Spin Resonance An RF Designer's Approach to Early Cancer Detection

Donhee Ham, Harvard University, Cambridge, MA

- 8:20 Integrated Radio-Frequency Biosensors for POC Applications Ali Hajimiri, Caltech, Pasadena, CA

- 8:40 BANning Low Power Radio Design Brian P. Otis, University of Washignton, Seattle

- 9:00 Wireless Telemetry Plays a Significant Role in Orchestrated Care: Concerto™/Virtuoso™ with MICS Frequency Band Javaid Masoud, Medtronic, Minneapolis, MN

- 9:20 Medical Imaging: RF Radio Design to the Rescue Kris Iniewski, CMOS Emerging Technologies, Vancouver, Canada

#### SE2: Is Fabless MEMS Fabulous?

### Organizer: Farrokh Ayazi, Georgia Institute of Technology, Atlanta, GA

#### Moderator: Christoph Hagleitner, IBM, Rüschlikon, Switzerland

Recent years have witnessed the maturity of MEMS in automotive safety applications and their penetration into cost-sensitive consumer markets. With the emergence of consumer applications for sensors and reconfigurable radio, the MEMS industry is at a growth inflection point. Many start-ups are trying to bring low-cost devices to market using a fab-less or a fab-lite business model. Despite this, successful commercialization stories are sparse among MEMS start-ups and are mostly related to the larger and more established companies that have commercialized MEMS after many years of costly internal research and development for high-price margin applications. When it comes to MEMS, is fabless fabulous? Or are in-house fabs invaluable? Are today's MEMS lowcost enough to compete and survive in consumer markets?

#### Panelists:

Janusz Brizek, LV Sensors, Emeryville, CA Kaigham J. Gabriel, Akustika, Pittsburgh, PA Michael Judy, Analog Devices, Cambridge, MA Edvard Kälvesten, Silex Microsystems, Järfälla, Sweden Arthur S. Morris, wiSpry, Irvine, CA

#### **PLENARY SESSION - INVITED PAPERS**

Chair: Timothy Tredwell, Carestream Health, Rochester, NY ISSCC Executive-Committee Chair

Associate Chair: William Bowhill, Intel, Hudson, MA ISSCC Program-Committee Chair

#### FORMAL OPENING OF THE CONFERENCE

8:15AM

#### 1.1 Leaner and Greener: Adapting to a Changing Climate of Innovation

8:30AM

#### René Penning de Vries, CTO, NXP Semiconductors, Eindoven, Netherlands

The semiconductor industry has been the enabling technology that has driven many huge changes in everyday life. Personal computing, mobile communications, Internet, and broadband technology, are obvious examples. Now, a new challenge is facing the industry – energy and power management – but not simply the concern for longer mobile battery life!

A new vision is needed for the semiconductor industry; how can our technologies help to improve everyone's use of energy to meet the challenges of climate change and limited supplies? Firstly, we need a vision of what can be achieved, in terms of how the semiconductor industry can make significant changes to the energy needs of different application sectors. Obvious targets are the sectors where large energy consumption is common, such as consumer-appliance, lighting, and automotive, and where there are large amounts of electronics, such as PCs and TVs, running continuously. Improved efficiency due to semiconductor technology can make a real difference. For every 1% saved in the world's electricity consumption, roughly 40 fewer power stations are required!

At the same time, we need a technological vision of how semiconductor technology must advance and evolve for more improvements to be realised. Device technologies, such as high voltage and high power, need to be combined with new sensors and control, while operating over extended temperature ranges to provide energy-conserving control and management of systems previously not economic to address. This plenary presentation will explore how the semiconductor industry can go beyond traditional approaches and make bigger reductions in the energy demands of the modern world.

#### 1.2 Adaptive Circuits for the 0.5-V Nanoscale CMOS Era 9:10AM

#### Kiyoo Itoh, Fellow, Hitachi Tokyo, Japan

Low-voltage scaling limitations are one of the major problems in the nanoscale era – they bring evermore-serious power crises with device scaling. The problems stem from the existence of two unscalable device parameters: The first is the high value of the lowest necessary threshold voltage ( $V_{t0}$ ) of MOSFETs needed to keep the subthreshold leakage low; The second is the variation in threshold ( $\Delta V_t$ ) that has increased in the nanoscale era. Due to these two inherent features of  $V_{t0}$  and  $\Delta V_t$ , the minimum usable power supply ( $V_{DD}$ ), namely,  $V_{min}$  increases with device scaling. The actual operating voltage  $V_{DD}$  is thus facing the 1-V wall in the 45-nm generation and is expected to rapidly increase with further scaling of poly-Si bulk MOSFETs.

Another problem in the nanoscale era, that is, the ever-higher interconnect resistance, is also closely related to the voltage-limitation problem at the chip and subsystem levels: It further increases the actual operating voltage, since, while it degrades the speed of everlarger chips, it reduces power-supply integrity by increasing power-supply droop and noise in power-supply lines. For the ULSI industry to continue to proliferate, the voltage-scaling-limitation problem must be solved in the 32-nm generation and beyond. This requires a multidisciplinary approach, since it covers various fields, such as, devices, circuits (digital and analog), and subsystems.

This Plenary talk will address issues related to adaptive circuits and relevant technologies intended to reduce  $V_{min}$  and ensure power-supply integrity.  $V_{min}$  reduction is described in the first half. After comparing  $V_{min}$  values for several blocks, namely, logic, SRAM and DRAM, state-of-the-art SRAM circuits which tackle the issue are reviewed. Then, devices and circuits to reduce the values of  $V_{min}$  to the sub-1-V region, such as  $\Delta V_r$ -scalable FinFETs and low- $V_{r0}$  low-leakage circuits utilizing the gate-source back-biasing scheme, are discussed. In the second half, the power-supply integrity issues are described. In addition to new architectures such as multi-core MPUs, and 3-D thermally conscious chip integration for compact subsystems, drastic reduction in memory-array area of small cores and chips is particularly vital to ensure integrity, since the array dominates their area. Thus, a logic-process-compatible FinFET DRAM cell, achieved using a unique cell and array selection scheme, is proposed. Finally, a scenario for achieving sub-0.5-V supply in nanoscale CMOS is presented.

#### ISSCC, SSCS, JSSCC, & IEEE AWARD PRESENTATIONS 9:50AM

BREAK 10:20AM

10:35AM

#### 1.3 The New Era of Scaling in an SoC World

#### Mark Bohr, Senior Fellow, Intel, Hillsboro, OR

Traditional MOSFET scaling served our industry well for about 30 years, until limits posed by leakage and total chip power were reached earlier in this decade. To overcome these limits we have entered a new era of scaling, where innovations in device materials and transistor structure are just as important as simple scaling of dimensions for achieving continued improvements in density and performance. Examples of these types of innovations began with the introduction of copper and low-resistivity interconnects, followed by strained-silicon transistors, and more recently, high- $\kappa$  dielectrics along with metal-gate transistors.

Circuit layout has also faced severe challenges in meeting high density and low variability as minimum feature sizes have scaled below the wavelength of light used for patterning. Lithography-enhancement techniques such as optical- proximity correction, phase-shift masks and gridded layout have kept us on track for feature-size scaling. Although traditional MOSFET scaling techniques have not been good for analog circuits due to degraded transistor gain  $g_m/g_{ds}$ , reduced dynamic range, and worse, transistor mismatch, modern microprocessors have successfully incorporated a larger number, and a wider range, of high-performance analog circuits than in the past due to circuit innovations.

Adaptive circuits have been employed to a greater degree to overcome device-variability limitations and to more finely tune performance and power characteristics. Some of the process and design techniques employed on new microprocessor products will be described along with research options being explored for the 22nm generation and beyond. The goal of these research efforts will be increasingly focused on SoC products that integrate a diverse set of device types, adapting to meet a broader range of product functions and applications than those that are available today!

#### 1.4 Kids Today! Engineers Tomorrow?

John Cohn, Fellow, IBM Systems and Technology Group, Essex Junction, VT

Imagine the next generation of engineers. What will they be like? Will there be enough of them worldwide? What will motivate them to join us in the profession we love?

This Plenary presentation will take a look at engineering-enrolment trends worldwide, and try to make sense of the numbers. We will explore the so called "engineering crisis", and understand what is going on. Is this a world issue, or "only" an issue in the West? Why are kids in certain parts of the world not joining our field? What are they doing instead? Does the answer lie in how society views and portrays our professions? If so, what can we, as practitioners, do to change those perceptions?

In this plenary presentation we will try to understand the real story behind these questions, from a worldwide perspective, and what they mean to the future of our industry. We will look at what motivates kids these days and explore how this resonates with the messages kids are hearing about engineering careers today. We will look at how we can help change the conversation around the engineering profession using a new set of messages and a new set of "Grand Challenges" based on world issues such as energy, climate and global sustainability.

Messages alone are not going to change the future! The only thing that will shape the future of our industry is you the engineer. We will take a look at how each of us has the opportunity to pass on our love and passion of our field to the next generation. We will look at outreach activities that you and your colleagues can start now to pass that passion along and to recharge your own batteries in the process. We will look at specific things you can begin doing to do in your own homes, schools, communities and nations and in the mass media and the Internet. We will also look at ways that you the engineer can use your influence in your own companies, universities and professional societies to magnify your efforts. We will include a few "shocking" demonstrations to drive these points home. Please come and begin helping us shape a better world by helping build the next generation of engineers. It is an important job...., and we are the only ones who can do it!

Conclusion 11:55AM

11:15AM

#### IMAGERS

#### Session Chair: Jan Bosiers, DALSA Professional Imaging, Eindhoven, Netherlands Associate Chair: Makoto Ikeda, University of Tokyo, Tokyo, Japan

#### 2.1 A 4-Side Tileable Back-Illuminated 3D-Integrated Mpixel CMOS Image Sensor

1:30 PM

V. Suntharalingam<sup>1</sup>, R. Berger<sup>1</sup>, S. Clark<sup>2</sup>, J. Knecht<sup>1</sup>, A. Messier<sup>1</sup>, K. Newcomb<sup>1</sup>, D. Rathman<sup>1</sup>, R. Slattery<sup>1</sup>, A. Soares<sup>1</sup>, C. Stevenson<sup>1</sup>, K. Warner<sup>1</sup>, D. Young<sup>1</sup>, L. Ang<sup>3</sup>, B. Mansoorian<sup>3</sup>, D. Shaver<sup>1</sup>

<sup>1</sup>MIT Lincoln Laboratory, Lexington, MA <sup>2</sup>Irvine Sensors, Costa Mesa, CA <sup>3</sup>Forza Silicon, Pasadena, CA

A 3D-integrated back-illuminated 1Mpixel CMOS image sensor tile includes a stack of 2×32-channel vertically integrated ADC chips, and requires 13.4 $\mu$ m of silicon perimeter to the pixel array. The tile and system connector design supports 4-side abuttability and burst data rates of 1Mpixel in 1ms.

#### 2.2 A Gamma, X-Ray and High-Energy-Proton Radiation-Tolerant CIS for Space Applications

2:00 PM

L. Carrara<sup>1</sup>, C. Niclass<sup>1</sup>, N. Scheidegger<sup>1</sup>, H. Shea<sup>1</sup>, E. Charbon<sup>1,2</sup> <sup>1</sup>EPFL, Lausanne, Switzerland <sup>2</sup>Delft University of Technology, Delft, Netherlands

This paper presents a  $0.35\mu$ m CIS that is tolerant to gamma, X-ray and 11MeV/60MeV proton radiation. Its core is an array of  $32\times32$  pixels each containing a static memory and a single-photon detector. A 2-gray-level frame is transfered in 1.2µs. The chip tolerates 1Mrad of gamma, 40krad of proton, and 1mGy of X-ray radiation. The dark-count-rate degradation is contained or negligible.

#### 2.3 A 4-Channel 20-to-300Mpixel/s Analog Front-End with Sampled Thermal Noise Below kT/C for Digital SLR Cameras

2:30 PM

*R. Kapusta*<sup>1</sup>, *E. Ibaragi*<sup>2</sup>, *K. Ni*<sup>3</sup>, *R. Wang*<sup>3</sup>, *H. Shinozak*<sup>2</sup>, *L. Singer*<sup>1</sup>, *K. Nakamura*<sup>1</sup> <sup>1</sup>Analog Devices, Wilmington, MA <sup>2</sup>Analog Devices, Tokyo, Japan <sup>3</sup>Analog Devices, Beijing, China

A 0.18µm CMOS 4-channel AFE for digital SLR cameras is reported that is optimized for clock rates of 5 to 75MS/s/channel and that uses nonlinear adaptive biasing based on clock frequency. Optimization techniques for a multi-channel system achieve -85dB crosstalk and 0.01% channel mismatch. Sub-kT/C sampling achieves 80dB DR and uses capacitors that are 60% smaller than normal.

Break 3:00 PM

#### 2.4 A 1/2.5-inch 8Mpixel CMOS Image Sensor with a Staggered Shared-Pixel Architecture and an FD-Boost Operation

3:15 PM

*N. Tanaka, J. Naruse, A. Mori, R. Okamoto, H. Yamashita, M. Monoi* Toshiba Semiconductor, Yokohama, Japan

A 1/2.5-inch 8Mpixel CMOS image sensor employs a staggered shared-pixel architecture to suppress Gr/Gb sensitivity imbalance. It also employs an FD-boost operation using the C<sub>GS</sub> and C<sub>GD</sub> of amplifier transistors to yield large FD capability and low dark random noise. It achieves a Gr/Gb sensitivity ratio of 99.7%, random noise of  $2.6e_{rms}$  and a pixel capacity of 7.7ke<sup>-</sup>.

#### 2.5 An SoC Combining a 132dB QVGA Pixel Array and a 32b DSP/MCU Processor for Vision Applications

3:45 PM

P-F. Rüedi, P. Heim, S. Gyger, F. Kaess, C. Arm, R. Caseiro, J-L. Nagel, S. Todeschini CSEM, Neuchâtel, Switzerland

An SoC combining a QVGA time-domain logarithmic pixel array, a 50MHz 32b DSP/MCU processor and a 128KB SRAM achieves a 132dB intra-scene DR encoded in 10b, representing 149 steps per decade. Computation of contrast magnitude and direction in the readout path allows for visual scene analysis. The SoC achieves an FPN of 0.51 LSB, power consumption of 80mW and a 44mm<sup>2</sup> area in 0.18µm CMOS.

#### 2.6 A 1/3.2-inch 3.3Mpixel CMOS Image Sensor with a Column-Signal-Addition Method Using a PMOS Column Amplifier

#### 4:15 PM

H. Takahashi, T. Itano, T. Watanabe, K. Iwata, H. Akabori, S. Takimoto, R. Mishima, I. Ueno, K. Sakurai, T. Ichikawa, G. Momma, S. Inoue Canon, Ayase, Japan

A 1/3.2-inch 3.3Mpixel CMOS image sensor is fabricated in a 0.15 $\mu$ m 1P3M CMOS process. A deep-photodiode-isolation pixel and PMOS column amplifier achieves 96 $\mu$ V/e<sup>-</sup> conversion gain, 7.2e's dark current at 60°C, and 2.5e<sup>-</sup><sub>rms</sub> random noise. The sensor has a column-level signal-addition mode that realizes 15500e<sup>-</sup>/lx-s sensitivity (green pixel) and interlace scan.

#### 2.7 A Charge-Multiplication CMOS Image Sensor Suitable for Low-Light-Level Imaging

#### 4:30 PM

R. Shimizu, M. Arimoto, H. Nakashima, K. Misawa, K. Suzuki, T. Ohno, Y. Nose, K. Watanabe, T. Ohyama, K. Tani

Sanyo Electric, Anpachi, Japan

A CIF-format charge-multiplication 0.35µm 2P4M CMOS image sensor with 10µm pixel pitch is presented. It can execute charge multiplication using impact ionization of photo-generated signals within each pixel. For a significant increase in SNR at low light levels, up to 60× charge multiplication is achieved at a readout speed of 100µs/frame.

#### 2.8 A Dual-Conversion-Gain Video Sensor with Dewarping and Overlay on a Single Chip

4:45 PM

A. R. Huggett<sup>1</sup>, C. Silsby<sup>2</sup>, S. Cami<sup>1</sup>, J. Beck<sup>2</sup>

<sup>1</sup>Aptina Imaging, Bracknell, United Kingdom; <sup>2</sup>Aptina Imaging, Corvallis, OR

A 47mm<sup>2</sup> video sensor SoC comprises a 60fps 640×480 array of dual-conversion-gain 5.6 $\mu$ m pixels with >80dB DR, noise floor of <1e<sup>-</sup><sub>rms</sub> and switchable sensitivities of 2.5V/lx·s or 11.9V/lx·s and corresponding PRNUs of 0.57% or 0.68%, a video processor for correcting optical warp of up to 96 lines together with perspective adjustment, and a video overlay circuit.

#### Conclusion 5:15 PM

20

#### MICROPROCESSOR TECHNOLOGIES

#### Session Chair: Sonia Leon, Sun Microsystems, Santa Clara, CA Associate Chair: Fabio Campi, STMicroelectronics, Agrate Brianza, Italy

#### 3.1 A 45nm 8-Core Enterprise Xeon® Processor

S. Rusu, S. Tam, H. Muljono, J. Stinson, D. Ayers, J. Chang, R. Varada, M. Ratta, S. Kottapalli Intel. Santa Clara. CA

An 8-core 16-thread enterprise Xeon® processor has 2.3B transistors in 9M 45nm CMOS. The I/O links use per-lane TX and RX compensation to enable operation up to 6.4GT/s. Vertical and horizontal spines keep the uncore clock skew under 19ps before engaging the compensation. Core and cache shut-off techniques are used to minimize leakage.

#### 3.2 A Family of 45nm IA Processors

*R. Kumar, G. Hinton* Intel, Hillsboro, OR

A family of next-generation IA processors with up to 8 cores, enhanced Core<sup>TM</sup> microarchitecture, 3-level caches and 2-way SMT is implemented in 45nm high- $\kappa$  metal-gate CMOS. The family has a coherent point-to-point link and integrates memory controller, power-management microcontroller and power-gate transistors and scales from sub-10 to 130W in mobile, desktop and server applications.

#### 3.3 A Chip-Stacked Memory for On-Chip SRAM-Rich SoCs and Processors

2:30 PM

H. Saito, M. Nakajima, T. Okamoto, Y. Yamada, A. Ohuchi, N. Iguchi, T. Sakamoto, K. Yamaguchi, M. Mizuno NEC. Kanagawa, Japan

NEC, Kanagawa, Japan

A dynamically reconfigurable memory chip with 3D integration is fabricated, in which on-chip memories of an SoC chip are moved to the memory chip to increase the efficiency of memory usage. Area overhead of network interconnects for the memory chip is reduced by 63% and the latency overhead by 43%. Signal lines between the two chips are directly connected by 10 $\mu$ m-pitch inter-chip electrodes.

Break 3:00 PM

## 3.4 Dynamic Frequency-Switching Clock System on A Quad-Core Itanium® Processor

3:15 PM

*A. Allen, J. Desai, D. Mulvihill, F. Verdico, F. Anderson* Intel, Fort Collins, CO

The clock system for a 700mm<sup>2</sup> 65nm quad-core Itanium<sup>®</sup> processor has a cascaded PLL architecture and enables dynamic frequency switching with a single-cycle switch penalty and minimal di/dt impact, which minimizes power-supply disturbance. This allows frequency-power optimization without stopping the clock.

2:00 PM

1:30 PM

#### 3.5 Secure AES Engine with A Local Switched-Capacitor Current Equalizer

#### C. Tokunaga, D. Blaauw

University of Michigan, Ann Arbor, MI

A 0.13 $\mu$ m CMOS AES engine uses a switched-capacitor current equalizer to reduce leakage of side-channel information through the power supply, improving security against secret-key attacks, such as DPA. The design has 7.2% area, 33% power and 2× performance overheads compared to differential logic and noise addition, which have 3× area, 4× power, and 4× performance penalties.

#### 3.6 A 4Gb/s/ch 356fJ/b 10mm Equalized On-chip Interconnect with Nonlinear Charge-Injecting Transmit Filter and Transimpedance Receiver in 90nm CMOS

4:15 PM

#### B. Kim, V. M. Stojanovic

Massachusetts Institute of Technology, Cambridge, MA

A link with 3-tap pre-distorted charge-injection transmit filter and transimpedance receiver in 90nm CMOS achieves 4Gb/s/ch intra-chip communication over 10mm-long global wires at 2 $\mu$ m link pitch, 356fJ/b energy cost, and transceiver area of 1760 $\mu$ m<sup>2</sup>. The *in situ* measured eye is 98mV and 50% UI at 4Gb/s.

#### 3.7 Dual-DLL-Based CMOS All-Digital Temperature Sensor for Microprocessor Thermal Monitoring

4:30 PM

*K. Woo<sup>1</sup>, S. Meninger<sup>2</sup>, T. Xanthopoulos<sup>2</sup>, E. Crain<sup>2</sup>, D. Ham<sup>1</sup>* <sup>1</sup>Harvard University, Cambridge, MA <sup>2</sup>Cavium Networks, Marlborough, MA

A CMOS all-digital temperature sensor for microprocessor thermal monitoring works by measuring temperature-dependent delays of CMOS inverters. It uses two fine-precision DLLs, occupies  $0.12 \text{mm}^2$ , and has a 5kS/s bandwidth at 7b resolution, dissipating 1.2mW. Measured errors for a  $0.13 \mu \text{m}$  CMOS implementation are -1.8 to 2.3°C across 0 to 100°C.

#### 3.8 Over One Million TPCC with a 45nm 6-Core Xeon® CPU

**4:45 PM**  *R. Kuppuswamy*<sup>1</sup>, *S. R. Sawant*<sup>1</sup>, *S. Balasubramanian*<sup>1</sup>, *P. Kaushik*<sup>1</sup>, *N. Natarajan*<sup>1</sup>, *J. D. Gilbert*<sup>2</sup> <sup>1</sup>Intel, Bangalore, India <sup>2</sup>Intel, Portland, OR

A monolithic 6-core Xeon® processor has 1.9B transistors in 9M 45nm CMOS with a 9MB L2 and 16MB L3 cache and exceeds 1M transactions/minute TPCC in 8-socket configuration. The FSB I/O circuits are implemented in the center of the die to reduce I/O latency. A low-leakage process variant with cache-sleep and shut-off modes enables low-power 6-core 65W and 4-core 50W variants.

Conclusion 5:15 PM

3:45 PM

#### **HIGH-SPEED DATA CONVERTERS**

#### Session Chair: Boris Murmann, Stanford University, Stanford, CA Associate Chair: Dieter Draxelmayr, Infineon Techologies, Villach, Austria

#### 4.1 A 12b 2.9GS/s DAC with IM3 <-60dBc Beyond 1GHz in 65nm CMOS

**1:30 PM** *C-H. Lin<sup>1</sup>, F. van der Goes<sup>2</sup>, J. Westra<sup>2</sup>, J. Mulder<sup>2</sup>, Y. Lin<sup>2</sup>, E. Arslan<sup>2</sup>, E. Ayranci<sup>2</sup>, X. Liu<sup>2</sup>, <i>K. Bult<sup>2</sup>* <sup>1</sup>Broadcom, Irvine, CA <sup>2</sup>Broadcom. Bunnik. Netherlands

A 12b 2.9GS/s current-steering DAC implemented in 65nm CMOS is presented, with an IM3 <-60dBc beyond 1GHz, while driving a  $50\Omega$  load with an output swing of 2.5V<sub>pp-diff</sub> and dissipating 188mW. The SFDR measured at 2.9GS/s is better than 60dB beyond 340MHz, while the SFDR measured at 1.6GS/s is greater than 60dB beyond 440MHz.

## 4.2 A 1.1V 50mW 2.5GS/s 7b Time-Interleaved C-2C SAR ADC in 45nm LP Digital CMOS

2:00 PM

*E. Alpman<sup>1,2</sup>, H. Lakdawala<sup>1</sup>, R. Carley<sup>2</sup>, K. Soumyanath<sup>1</sup>* <sup>1</sup>Intel, Hillsboro, OR <sup>2</sup>Carnegie Mellon University, Pittsburgh, PA

A 7b 2.5GS/s Nyquist ADC is implemented in digital 45nm LP-CMOS by time-interleaving 16 C-2C SAR ADCs with radix, offset, gain and timing calibration. The ADC achieves >6.1 ENOB and <-49dBc SFDR for a single SAR, and >5.4 ENOB and <-43dBc SFDR for the time-interleaving SAR up to the Nyquist frequency. The ADC consumes 50mW on a 1.1V supply and achieves an FOM of 480fJ/conversion-step.

#### 4.3 A 1.8V 1.0GS/s 10b Self-Calibrating Unified-Folding-Interpolating ADC with 9.1 ENOB at Nyquist Frequency

2:30 PM

R. C. Taft<sup>1</sup>, P. A. Francese<sup>1</sup>, M. R. Tursi<sup>1</sup>, O. Hidri<sup>1</sup>, A. MacKenzie<sup>2</sup>, T. Hoehn<sup>1</sup>, P. Schmitz<sup>1</sup>, H. Werker<sup>1</sup>, A. Glenny<sup>3</sup>

<sup>1</sup>National Semiconductor, Unterhaching, Germany <sup>2</sup>National Semiconductor, Greenock, United Kingdom <sup>3</sup>National Semiconductor, Santa Clara, CA

A 0.18 $\mu$ m CMOS folding-interpolating ADC that eliminates the separate coarse channel is presented. The single unified channel consists of cascaded folding stages with embedded comparators in which each stage acts as the coarse channel for the following one. The dual 1.8V 1.0GS/s 10b ADC yields ±0.2 LSB DNL and 9.1 ENOB at Nyquist.

Break 3:00 PM

#### 4.4 A 5b 800MS/s 2mW Asynchronous Binary-Search ADC in 65nm CMOS

3:15 PM

*Y-Z. Lin, S-J. Chang, Y-T. Liu, C-C. Liu, G-Y. Huang* National Cheng-Kung University, Tainan, Taiwan

A 5b asynchronous binary-search ADC with reference range prediction uses 2n-1 rather than 2<sup>n</sup>-1 comparators. It also includes a passive THA, a reference ladder, 56 switches and static logic. The active area is  $120 \times 150 \mu m^2$  in 65nm CMOS. The ADC consumes 1.97mW from a 1V supply. At 800MS/s the ENOB is 4.45b and the ERBW is 500MHz. The FOM is 113fJ/conversion-step.

#### 4.5 A 600MS/s 30mW 0.13µm CMOS ADC Array Achieving Over 60dB SFDR with Adaptive Digital Equalization

3:45 PM

W. Liu<sup>1</sup>, Y. Chang<sup>1,2</sup>, S-K. Hsien<sup>1,3</sup>, B-W. Chen<sup>3</sup>, Y-P. Lee<sup>3</sup>, W-T. Chen<sup>3</sup>, T-Y. Yang<sup>3</sup>, G-K. Ma<sup>3</sup>, Y. Chiu<sup>1</sup>

<sup>1</sup>University of Illinois, Urbana-Champaign, IL

<sup>2</sup>Jilin University, Changchun, China

<sup>3</sup>Industrial Technology Research Institute, Hsinchu, Taiwan

A 600MS/s 10-way time-interleaved SAR ADC array is fabricated in 0.13µm CMOS. Digital background equalization adaptively corrects the gain, offset, and linearity mismatch in the array, assisted by an algorithmic ADC. The prototype achieves 47.3dB peak SNDR and 65.2dB peak SFDR, while dissipating 30mW from a 1.2V supply.

#### 4.6 A 10b 500MHz 55mW 90nm CMOS ADC

#### 4:15 PM

*A. Verma, B. Razavi* University of California, Los Angeles, CA

A pipelined ADC consisting of 14 stages calibrates capacitor mismatch, and nonlinearity and gain error of opamps using an RDAC with 11b linearity. Employing a 2-stage opamp with a BW of 10GHz and a gain of 25, the 90nm digital CMOS ADC achieves a DNL of 0.4 LSB, an INL of 1 LSB and an SNDR of 53dB for a 233MHz input, while drawing 55mW from a 1.2V supply. The FOM is 0.3pJ/conversion-step.

#### 4.7 A 16b 125MS/s 385mW 78.7dB SNR CMOS Pipelined ADC

S. Devarajan, L. Singer, D. Kelly, S. Decker, A. Kamath, P. Wilkins Analog Devices. Wilmington. MA

A 16b 125MS/s pipelined ADC implemented in a  $0.18\mu$ m CMOS process achieves an SNR of 78.7dB, an SNDR of 78.6dB and an SFDR of 96dB with a 30MHz input, while maintaining SNR >76dB and SFDR >80dB up to 150MHz with a clock jitter of 65fs. The ADC has a SHA-less 4b front-end and includes digital calibration and dither to improve small-signal linearity. The ADC consumes 385mW from a 1.8V supply.

Conclusion 5:15 PM

4:45 PM

#### POTPOURRI: PLL, OPTICAL, DSL

#### Session Chair: Larry DeVito, Analog Devices, Wilmington, MA Associate Chair: Miki Moyal, Intel, Haifa, Israel

#### 5.1 A 7.1mW 10GHz All-Digital Frequency Synthesizer with Dynamically Reconfigurable Digital Loop Filter in 90nm CMOS

S-Y. Yang, W-Z. Chen

National Chiao Tung University, Hsinchu, Taiwan

A 10GHz all-digital frequency synthesizer with dynamic loop filter is presented. With less than 6.9µs locking time, the measured rms jitter from a 9.92GHz carrier is 0.9ps. A skew-compensated phase accumulator is proposed for high-speed and low-power operation. The core circuits consume 7.1mW. Fabricated in 90nm CMOS, the chip occupies 0.902mm<sup>2</sup>.

#### 5.2 Subharmonically Injection-Locked PLLs for Ultra-Low-Noise Clock Generation

2:00 PM

1:30 PM

*J. Lee<sup>1</sup>, H. Wang<sup>1</sup>, W-T. Chen<sup>2</sup>, Y-P. Lee<sup>2</sup>* <sup>1</sup>National Taiwan University, Taipei, Taiwan <sup>2</sup>Industrial Technology Research Institute, Hsinchu, Taiwan

A complete analysis of subharmonically injection-locked PLLs explains the noise-shaping phenomenon, and provides a model to predict the output phase noise. Two 20GHz PLLs based on the proposed theory are designed and fabricated in 90nm CMOS. The first chip achieves 149fs<sub>ms</sub> jitter while consuming 38mW from a 1.3V supply. The second prototype exhibits  $85fs_{ms}$  jitter with a power dissipation of 105mW.

#### 5.3 Bang-Bang Digital PLLs at 11 and 20GHz with sub-200fs Integrated Jitter for High-Speed Serial Communication Applications

2:30 PM

A. Rylyakov, J. Tierno, H. Ainspan, J-O. Plouchart, J. Bulzacchelli, Z. Toprak, D. Friedman IBM T. J. Watson, Yorktown Heights, NY

Two digital PLLs, realized in 65nm CMOS, feature a low-latency low-gain proportional path control and dynamic DCO steps with half-integer spacing. Time-domain  $\Delta\Sigma$  modulation of the reference clock enables control of bang-bang PFD gain and PLL bandwidth. LC-DCO tuning ranges are 8.1 to 11.8GHz and 16.4 to 22.4GHz. The rms jitter, integrated from f<sub>c</sub>/1667 to f<sub>c</sub>/2, is 140fs<sub>ms</sub> at 11GHz and 190fs at 20GHz.

#### 5.4 0.9mW 7GHz and 1.6mW 60GHz Frequency Dividers with Locking-Range Enhancement in 0.13µm CMOS

2:45 PM

S. Rong, W. Ng, H. Luong

Hong Kong University of Science and Technology, Hong Kong, China